## Proposed Draft

# Serial ATA International Organization

Version 0.2 4/30/2007

## Serial ATA Revision 2.6 ECN # 012 Title: Cable & Connector Retention

This is an internal working document of the Serial ATA International Organization. As such, this is not a completed standard and has not been approved. The Serial ATA International Organization may modify the contents at any time. This document is made available for review and comment only.

Permission is granted to the Promoters, Contributors and Adopters of the Serial ATA International Organization to reproduce this document for the purposes of evolving the technical content for internal use only without further permission provided this notice is included. All other rights are reserved and may be covered by one or more Non Disclosure Agreements including the Serial ATA International Organization participant agreements. Any commercial or for-profit replication or republication is prohibited. Copyright © 2000-2007 Serial ATA International Organization. All rights reserved.

This Draft Specification is NOT the final version of the Specification and is subject to change without notice. A modified, final version of this Specification ("Final Specification") when approved by the Promoters will be made available for download at this Web Site: http://www.serialata.org.

THIS DRAFT SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NON-INFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE. Except for the right to download for internal review, no license, express or implied, by estopple or otherwise, to any intellectual property rights is granted or intended hereunder.

THE PROMOTERS DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF ANY PROPRIETARY RIGHTS, RELATING TO USE OF INFORMATION IN THIS DRAFT SPECIFICATION. THE PROMOTERS DO NOT WARRANT OR REPRESENT THAT SUCH USE WILL NOT INFRINGE SUCH RIGHTS.

THIS DOCUMENT IS AN INTERMEDIATE DRAFT FOR COMMENT ONLY AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

\* Other brands and names are the property of their respective owners.

Copyright © 2005-2007 Serial ATA International Organization. All rights reserved.

### **Author Information**

| Author Name      | Company | Email address           |

|------------------|---------|-------------------------|

| Jerry D. Kachlic | Molex   | Jerry.kachlic@molex.com |

## **Workgroup Chair Information**

| Workgroup (Phy, Digital, etc) | Chairperson Name | Email address            |

|-------------------------------|------------------|--------------------------|

| cabcon                        | Frank Chu        | Frank.Chu@Hitachigst.com |

### **Document History**

| Version | Date       | Comments                                            |

|---------|------------|-----------------------------------------------------|

| 0       | 8/10/2006  | Initial release.                                    |

| 0.1     | 10/11/2006 | Revised figures and added explanation of GD&T usage |

| 0.2     | 4/30/2007  | Re-issued and reformatted for Rev. 2.6              |

|         |            |                                                     |

|         |            |                                                     |

|         |            |                                                     |

|         |            |                                                     |

|         |            |                                                     |

|         |            |                                                     |

#### 1 Introduction

The original SATA connector set has been found to have a tolerance overlap condition of the features which provide cable retention. These features are defined as a "bump" on the cable receptacle and a "slot" on the plug. The tolerance stack of feature size and feature location results in an overlap condition which prevents the bump from engaging with the slot.

#### 2 Technical Specification Changes

In order to minimize impact to existing products in the market, the following changes will be made to the feature location tolerances. The proposed changes make use of Geometric Dimensioning & Tolerancing (GD&T) by utilizing Maximum Material Condition (MMC), the new tolerancing scheme allows "bonus" tolerance when features are less than the maximum allowable size.

Glossary:

GD&T = Geometric Dimensioning & Tolerancing MMC = Maximum Material Condition WRT = with respect to

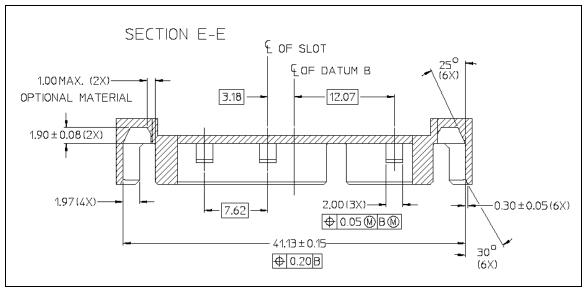

#### 2.1 Figure 27 – Device plug connector

Section E-E

Delete dimensions for locations of slots (7.05mm & 5.78mm)

Replace with basic dimensions from Centerline of Datum B to Centerlines of Slot Change 7.62 dimension to basic dimension

Add Geometric Tolerance Control frame to feature size.

GD&T = True position of 0.05mm @ MMC, WRT Datum B @ MMC

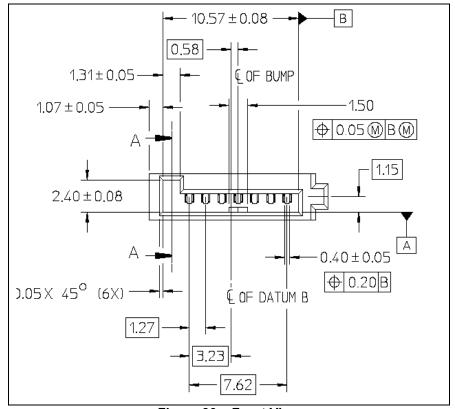

#### 2.2 Figure 30 – Cable receptacle connector interface dimensions

Front View

Delete dimension for bump location (4.71mm)

Replace with basic dimension from Centerline of Datum B to Centerline of Bump

Add Geometric Tolerance Control frame to feature size.

GD&T = True position of 0.05mm @ MMC, WRT Datum B @ MMC

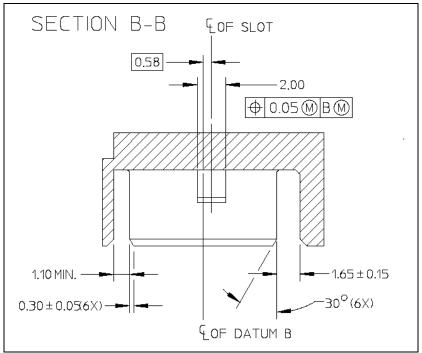

#### 2.3 Figure 32 – Host signal plug connector interface dimensions

Section B-B

Delete dimension for slot location (5.78mm)

Replace with basic dimension from Centerline of Datum B to Centerline of Slot Add Geometric Tolerance Control frame to feature size.

GD&T = True position of 0.05mm @ MMC, WRT Datum B @ MMC

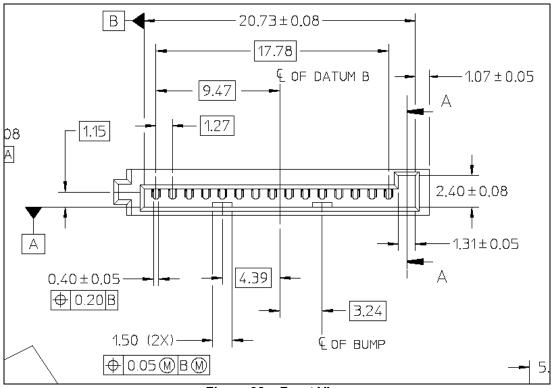

#### 2.4 Figure 38 – Power receptacle connector interface dimensions

Front View

Delete dimensions for locations of bump (5.98mm & 7.62mm)

Replace with basic dimensions from Centerline of Datum B to Centerlines of Bump Add Geometric Tolerance Control frame to feature size.

GD&T = True position of 0.05mm @ MMC, WRT Datum B @ MMC

Figure 27 - Section E-E

Figure 30 – Front View

Figure 32 - Section B-B

Figure 38 – Front View