# Proposed Draft

# Serial ATA International Organization

Version 0.90 Apr\_13, 2011

## Serial ATA Revision 3.0 ECN #053 Title : Gen-III (6Gbps) RiseTime Specification Change

This is an internal working document of the Serial ATA International Organization. As such, this is not a completed standard and has not been approved. The Serial ATA International Organization may modify the contents at any time. This document is made available for review and comment only.

Permission is granted to the Promoters, Contributors and Adopters of the Serial ATA International Organization to reproduce this document for the purposes of evolving the technical content for internal use only without further permission provided this notice is included. All other rights are reserved and may be covered by one or more Non Disclosure Agreements including the Serial ATA International Organization participant agreements. Any commercial or for-profit replication or republication is prohibited. Copyright © 2000-2011 Serial ATA International Organization. All rights reserved.

This Draft Specification is NOT the final version of the Specification and is subject to change without notice. A modified, final version of this Specification ("Final Specification") when approved by the Promoters will be made available for download at this Web Site: http://www.serialata.org.

THIS DRAFT SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NON-INFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE. Except for the right to download for internal review, no license, express or implied, by estopple or otherwise, to any intellectual property rights is granted or intended hereunder.

THE PROMOTERS DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF ANY PROPRIETARY RIGHTS, RELATING TO USE OF INFORMATION IN THIS DRAFT SPECIFICATION. THE PROMOTERS DO NOT WARRANT OR REPRESENT THAT SUCH USE WILL NOT INFRINGE SUCH RIGHTS.

THIS DOCUMENT IS AN INTERMEDIATE DRAFT FOR COMMENT ONLY AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

\* Other brands and names are the property of their respective owners.

Copyright © 2005-2011 Serial ATA International Organization. All rights reserved.

# **Author Information**

| Author Name   | Company           | Email address           |

|---------------|-------------------|-------------------------|

| Serge Bedwani | INTEL Corporation | serge.bedwani@intel.com |

# Workgroup Chair Information

| Workgroup (Phy, Digital,<br>etc) | Chairperson Name | Email address      |

|----------------------------------|------------------|--------------------|

| Phy                              | Chuck Hill       | cphill@altaeng.com |

## **Document History**

| Version | Date      | Comments                                            |

|---------|-----------|-----------------------------------------------------|

| 0.72    | 3/31/2011 | Initial release.                                    |

| 0.9     | 4/13/2011 | Updated with Waveform Data – S.Bedwani, John Calvin |

|         |           |                                                     |

|         |           |                                                     |

|         |           |                                                     |

|         |           |                                                     |

|         |           |                                                     |

### 1 Introduction

- Problem Statement: With the advent of significantly more FR4 signaling loss at 6Gbps, given the I/O congestion at the SATA 6Gbps Host-Controller (Platform-Controller Hub), and given the customer demands for desktop/server usage models requiring 6-inches of FR4-trace from the SATA 6Gbps-Host interface to the SATA connectors, the loss profiles at 6Gbps make it impossible to achieve edge-rates of 68ps.

- As the rise-time is compromised by longer traces dictated by the above usage models, even with a 35-38ps edge-rate at the component, we are unable to meet the current 68ps iSATA maximum (6Gbps) at the Tx-Compliance point, even for a shorter than required 4-in trace-length.

- Despite this inability to meet the 68ps Max.RiseTime requirement for 6Gbps iSATA, using optimized signaling de-emphasis techniques, the transmitter circuits under worst-case physical scenarios (process, voltage, temperature, and Impedance combinations) are able to guarantee the minimum signaling levels after the Compliance-Interconnect-Connect (CIC) to satisfy the iSATA requirements of 200mV at the Device Rx-Compliance Point.

- Assumptions that there is no implementation required use of Tx de-emphasis to meet iSATA signaling criteria at 6Gbps are incorrect, thus enforcement of the max rise-time limit of 68ps for product is not possible for the market required intended usage models.

- As described, it is important to acknowledge that Tx de-emphasis increased ratios (Transition-Bits to Non-Transition-Bit amplitudes) more than compensate for the attenuated energy, or slower risetime at the compliance points. Thus, de-emphasis levels become the dominating factor required for reducing ISI, optimizing amplitude, thru the various interconnect segments making up the iSATA 6Gbps interface.

**Remedy:** We are requesting that maximum Tx Risetime iSATA signaling levels at the iSATA Rx-Compliance point for the Device-side be relaxed from 68ps to 80ps

## 2.0 Specification Engineering Change Notice

## 2.1 Description of Change

### Section 7.2.1 Physical Layer Requirements Tables

|                                                        |            |                   |                          |               |              |       |          | -     | •                              |                                |                                     |

|--------------------------------------------------------|------------|-------------------|--------------------------|---------------|--------------|-------|----------|-------|--------------------------------|--------------------------------|-------------------------------------|

|                                                        | Units      | nits Limit        | Electrical Specification |               |              |       |          |       |                                |                                |                                     |

| Parameter                                              |            |                   | Gen1i                    | Gen1m         | Gen1x        | Gen2i | Gen2m    | Gen2x | Gen 3i                         | Detail<br>Cross-Ref<br>Section | Measurement<br>Cross-Ref<br>Section |

|                                                        |            | Min               | 400                      | 400           | 400          | 400   | 400      | 400   | -                              |                                | 7.4.5                               |

| V <sub>diffTX</sub> ,                                  |            | Min               | -                        | -             | -            | -     | -        | -     | 240                            | ]                              | 7.4.3                               |

| TX Differential                                        | mVppd      | Nom               | 50                       | )0            | -            |       | -        |       | -                              | 7.2.2.2.7                      | 7.4.5                               |

| Output Voltage                                         |            | Max               | 60                       | )0            | 1600         | 70    | 0        | 1600  | -                              | 1                              |                                     |

|                                                        |            | Max               | -                        |               | -            | -     |          | -     | 900                            |                                | 7.4.3                               |

| UI <sub>VminTX</sub> ,                                 | UI         |                   | 0.45-                    | 0.55          | 0.5          | 0.45- | 0.55     | 0.5   | -                              |                                | 7.4.5                               |

| TX Minimum<br>Voltage<br>Measurement<br>Interval       |            |                   | -                        |               | -            | -     |          | -     | 0.50                           | 7.2.2.2.8                      | 7.4.3.2                             |

| t <sub>20-80⊺X</sub> ,<br>TX Rise/Fall Time            | ps<br>(UI) | Min<br>20-<br>80% | 100 (                    | (.15 <b>)</b> | 67<br>(.10)  | 6     | 67 (.20) | )     | 33 (0.20)                      | 7.2.2.2.9                      | 7.4.4                               |

|                                                        |            | Max<br>20-<br>80% | 273                      | (.41)         | 273<br>(.41) | 1:    | 36 (.41  | )     | <del>- 68 (0.41) -</del><br>80 | 1.2.2.2.0                      | 7.4.4                               |

| t <sub>skew⊺X</sub> ,<br>TX Differential<br>Skew       | ps         | Max               |                          | 20            |              | 20    |          | 15    | 20                             | 7.2.2.2.10                     | 7.4.15                              |

| V <sub>cm,acTX</sub> ,<br>TX AC Common<br>Mode Voltage | mVp-p      | Мах               |                          | -             |              | 50    |          | -     | -                              | 7.2.2.2.11                     | 7.4.20                              |

#### Table 31 - Transmitted Signal Requirements

# Additional Details & Background Material

Max. Risetime at Host Tx Compliance Point

- Submitted [80ps for iSATA-6Gbps]

- Signaling-levels & Rise-times delivered to Host Tx-Compliance Points (INTEL) Justification based on Common Usage models – specifically additional trace-path-length on Host-side of the interface + **ISATA** ٠

- 6" motherboard-trace(FR4) to iSATA connector  $\rightarrow$  1.0m-cable  $\rightarrow$  HDD (~2" to 3" FR4)

- Direct-Connect ٠

- 8"-10" motherboard-trace(FR4) to iSATA connector → HDD

Definition of this interest.

- Definition of this interconnect usage model may accommodate Polyimid-FLEX[~5"] included in total length

- iSATA with Short-Backplane Interconnect

- 6" motherboard-trace(FR4) to iSATA connector  $\rightarrow$  0.5m-cable  $\rightarrow$  ~3.5" Backplane(FR4 or Low-Loss)  $\rightarrow$  HDD

- eSATA

- 6" motherboard-trace(FR4) to eSATA connector  $\rightarrow$  2.0m-cable  $\rightarrow$  HDD (~2" to 3" FR4)

#### Figure 1 - iSATA Usage Models and Signaling Complexities

### Rise-time / Fall-time at 6Gbps

- As the trace-lengths extending from the PCH to the <u>iSATA</u> connector are increased to the 6" target usage model, the measured rise-times at that <u>Tx</u>-Compliance point will increase.

- Inter-Symbol Interference jitter through the interconnect boundaries and segments has the following 3 components:

- Low-pass filter component due to the insertion-loss of the interconnect path Reflections and related distortions due to the characteristics of the Impedance boundary and change in coupling from 1-segment to the next segment

- Dispersion, where the signal-wave frequency components propagate at different speeds through the media

- . Slower incident rise-/fall-times into the interconnect segments will result in increased ISI jitter, thus requires Tx pre-emphasis/ de-emphasis

- As the iSATA specification does not specify pre-emphasis/de-emphasis the amplitude is achieved by the Host and devices calibrating their pre-emphasis ratios.

- Pre-emphasis signaling ratios selected are determined by the length of the interconnect from PCH to Connector, and the cable-losses to achieve best quality signaling through the interconnect path. +

- Metrics determining the optimal pre-emphasis/de-emphasis ratio are measured at the end of the Interconnect-path on the signal delivered to the Rx-Compliance Point +

- ISI jitter is minimized by proper de-emphasis ratios -- note, that this jitter is high-frequency data-dependent jitter "Lone-Bit" Amplitude, as well as the Amplitude of those transition-bits following the longest-runlengths allowed by 8B10B encoding is increased by the pre-emphasis scheme.

- .

- The important optimization goal is achieved by observing the "BIT-UNIFORMITY" of the amplitude of sequence of bits

- + Note:

- Analog pre-emphasis techniques typically implement "half-bit" pre-emphasis, rather than "full-bit" pre-emphasis as do digital techniques. "Half-bit" pre-emphasis is not as effective as "Full-Bit" pre-emphasis.

- To achieve the equivalent ISI reduction, or to achieve the desired amplitude optimization, a higher pre-emphasis ratio may be needed for the half-bit pre-emphasis topologies.

| Board Name | Speed  | VT Corner | Pattern | Port | Cable |      | Contraction of the second | RiseTime<br>_Max | FallTime<br>_Max |

|------------|--------|-----------|---------|------|-------|------|---------------------------|------------------|------------------|

| Rose City  | 6 Gbps | Slow      | LFTP    | 0    | 0m    | LowZ | 4044 MIL                  | 77.68            | 75.5             |

| Meridian   | 6 Gbps | Low       | LFTP    | 0    | 0m    | LowZ | 5997MIL                   | 77.21            | 76.92            |

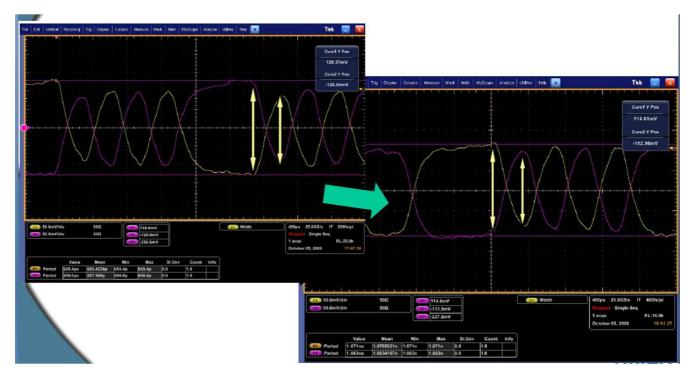

Figure 2 - Illustrates "Bit-Uniformity" Adjustment - De-Emphasis Optimization minimizing ISI

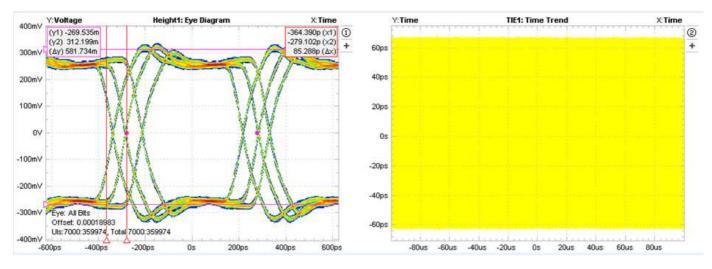

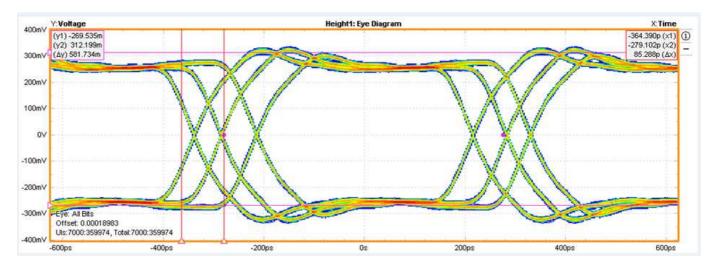

Figure 3 - 6Gbps LFTP Waveform 6-in

Figure 4 – 6Gbps LFTP Waveform 6-in (Zoom)

| × | Description            | Mean        | Std Dev     | Max         | Min         | р-р         | Population | Max-cc      | Min-cc       |

|---|------------------------|-------------|-------------|-------------|-------------|-------------|------------|-------------|--------------|

| × | TIE1, Math1            | -420.83fs   | 50.796ps    | 68.518ps    | -63.909ps   | 132.43ps    | 359614     | 128.54ps    | -74.571ps    |

| × | Current Acquisition    | -420.83fs   | 50.796ps    | 68.518ps    | -63.909ps   | 132.43ps    | 359614     | 128.54ps    | -74.571ps    |

| × | Height1, Math1         | 467.07mV    | 0.0000V     | 467.07mV    | 467.07mV    | 0.0000V     | 1          | 0.0000V     | 0.0000V      |

| × | Current Acquisition    | 467.07mV    | 0.0000V     | 467.07mV    | 467.07mV    | 0.0000V     | 1          | 0.0000V     | V00000       |

| × | TJ@BER1, Math1         | 135.60ps    | 0.0000s     | 135.60ps    | 135.60ps    | 0.0000s     | 1          | 0.0000s     | 0.0000s      |

| × | Current Acquisition    | 135.60ps    | 0.0000s     | 135.60ps    | 135.60ps    | 0.0000s     | 1          | 0.0000s     | 0.0000s      |

| × | Rise Time1, Math1      | 70.321ps    | 1.8419ps    | 77.127ps    | 64.309ps    | 12.819ps    | 179806     | 10.128ps    | -8.7025ps    |

| × | Current Acquisition    | 70.321ps    | 1.8419ps    | 77.127ps    | 64.309ps    | 12.819ps    | 179806     | 10.128ps    | -8.7025ps    |

| × | Fall Time1, Math1      | 70.216ps    | 1.5676ps    | 76.373ps    | 63.983ps    | 12.390ps    | 179806     | 8.8641ps    | -8.7888ps    |

| × | Current Acquisition    | 70.216ps    | 1.5676ps    | 76.373ps    | 63.983ps    | 12.390ps    | 179806     | 8.8641ps    | -8.7888ps    |

| × | Cycle Pk-Pk1, Math1    | 626.17mV    | 11.075mV    | 665.60mV    | 596.00mV    | 69.600mV    | 359972     | 37.600mV    | -42.400mV    |

| × | Current Acquisition    | 626.17mV    | 11.075mV    | 665.60mV    | 596.00mV    | 69.600mV    | 359972     | 37.600mV    | -42.400mV    |

| × | Rise Slew Rate1, Math1 | 4.3300V/ns  | 113.17mV/ns | 4.7315V/ns  | 3.9451V/ns  | 786.38mV/ns | 179987     | 526.73mV/ns | -634.10mV/ns |

| × | Current Acquisition    | 4.3300V/ns  | 113.17mV/ns | 4.7315V/ns  | 3.9451V/ns  | 786.38mV/ns | 179987     | 526.73mV/ns | -634.10mV/ns |

| × | Fall Slew Rate1, Math1 | -4.3356V/ns | 96.532mV/ns | -3.9841V/ns | -4.7555V/ns | 771.49mV/ns | 179987     | 553.07mV/ns | -537.78mV/ns |

| × | Current Acquisition    | -4.3356V/ns | 96.532mV/ns | -3.9841V/ns | -4.7555V/ns | 771.49mV/ns | 179987     | 553.07mV/ns | -537.78mV/ns |

### Measurement Results

Figure 5 - 6Gbps LFTP Waveform 6-in (Measurement Results)