# Serial ATA International Organization

Revision 1.00RC2 22-June 2006

Serial ATA Interoperability Program

Agilent Technologies, Inc. Method of Implementation (MOI)

Document for SATA PHY, TSG & OOB Measurements

(Real-time DSO Measurements)

This document is provided "AS IS" and without any warranty of any kind, including, without limitation, any express or implied warranty of non-infringement, merchantability or fitness for a particular purpose. In no event shall SATA-IO or any member of SATA-IO be liable for any direct, indirect, special, exemplary, punitive, or consequential damages, including, without limitation, lost profits, even if advised of the possibility of such damages.

This material is provided for reference only. The Serial ATA International Organization does not endorse the vendors' equipment outlined in this document.

# TABLE OF CONTENTS

| TABLE OF CONTENTS                                             | 2  |

|---------------------------------------------------------------|----|

| MODIFICATION RECORD                                           | 3  |

| ACKNOWLEDGMENTS                                               | 4  |

| INTRODUCTION                                                  | 5  |

| GROUP 1: PHY GENERAL REQUIREMENTS                             | 7  |

| TEST PHY-01 - UNIT INTERVAL                                   | 8  |

| TEST PHY-02 – Frequency Long Term Stability                   |    |

| TEST PHY-03 - SPREAD-SPECTRUM MODULATION FREQUENCY            |    |

| TEST PHY-04 - SPREAD-SPECTRUM MODULATION DEVIATION            | 12 |

| GROUP 2: PHY TRANSMITTED SIGNAL REQUIREMENTS                  | 14 |

| TEST TSG-01 - DIFFERENTIAL OUTPUT VOLTAGE                     | 15 |

| TEST TSG-02 - RISE/FALL TIME                                  |    |

| Test TSG-03 - Differential Skew                               |    |

| TEST TSG-04 - AC COMMON MODE VOLTAGE                          |    |

| TEST TSG-05 - RISE/FALL IMBALANCE                             |    |

| TEST TSG-06 - AMPLITUDE IMBALANCE                             |    |

| TEST TSG-07 - TJ AT CONNECTOR, DATA, 5UI                      |    |

| TEST TSG-08 - DJ AT CONNECTOR, DATA, 5UI                      |    |

| TEST TSG-09 - TJ AT CONNECTOR, DATA, 250UI                    |    |

| TEST TSG-10 - DJ AT CONNECTOR, DATA, 250UI                    |    |

| TEST TSG-11 - TJ AT CONNECTOR, CLOCK, 500                     |    |

|                                                               |    |

| GROUP 3: PHY OOB REQUIREMENTS                                 | 39 |

| TEST OOB-01 – OOB SIGNAL DETECTION THRESHOLD                  | 40 |

| TEST OOB-02 – UI DURING OOB SIGNALING                         |    |

| TEST OOB-03 – COMINIT/RESET AND COMWAKE TRANSMIT BURST LENGTH |    |

| TEST OOB-04 – COMINIT/RESET TRANSMIT GAP LENGTH               |    |

| TEST OOB-05 – COMWAKE TRANSMIT GAP LENGTH                     |    |

| TEST OOB-06 – COMWAKE GAP DETECTION WINDOWS                   |    |

| TEST OOB-07 – COMINIT GAP DETECTION WINDOWS                   | 54 |

| APPENDIX A – INFORMATION ON REQUIRED RESOURCES                | 57 |

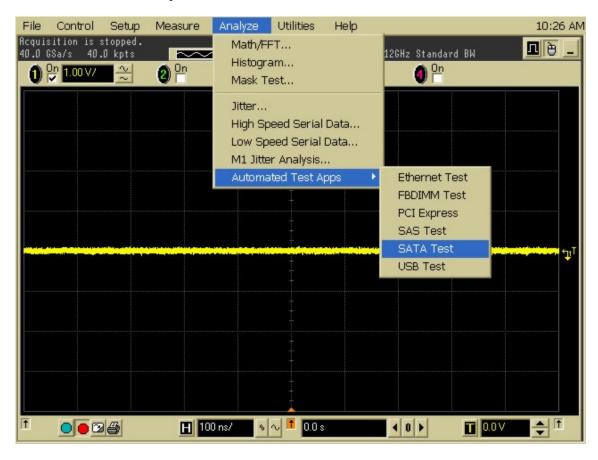

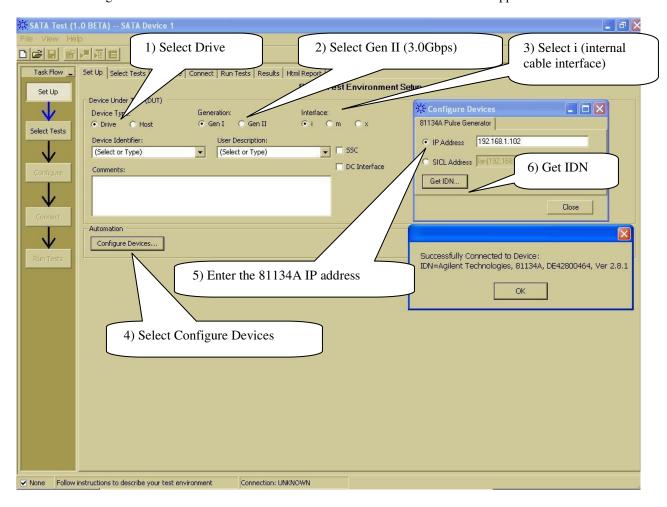

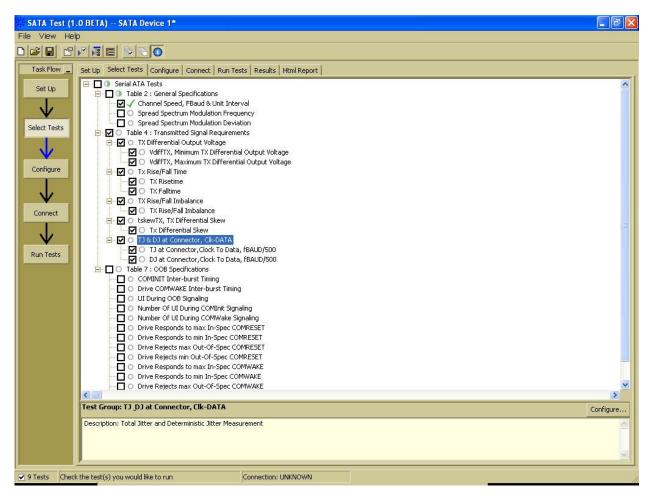

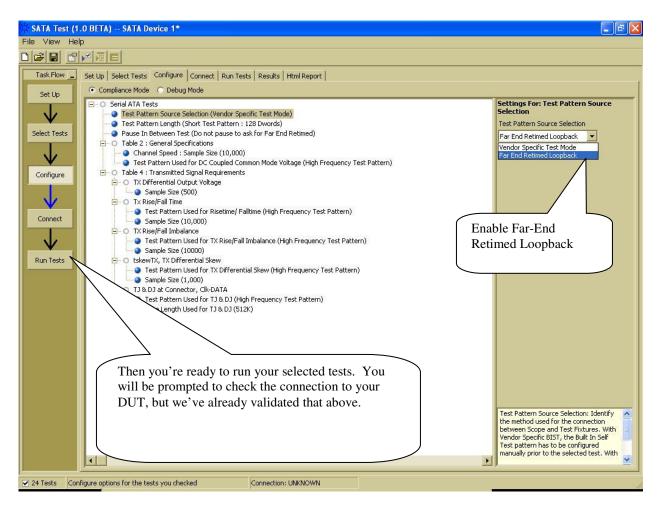

| Example N5411A Device Test Initial Setup Procedure            | 58 |

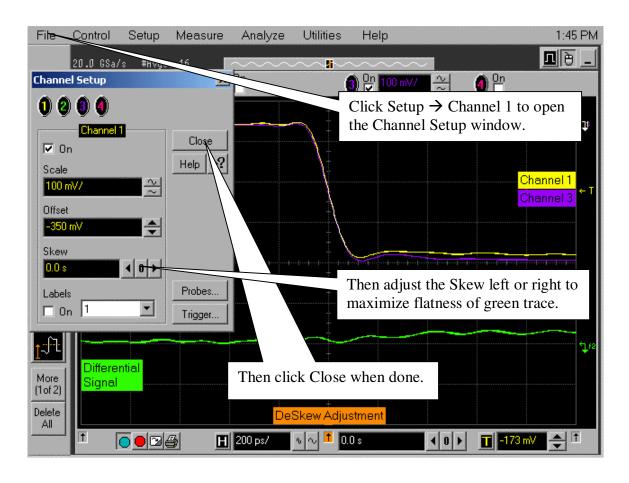

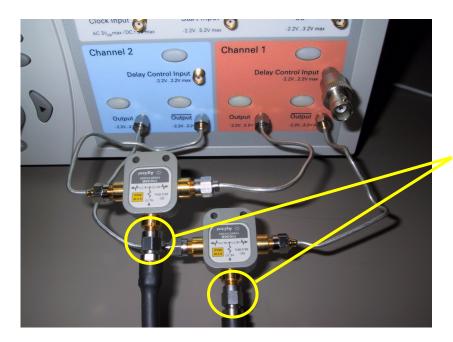

| CABLE DESKEW PROCEDURE                                        | 62 |

## MODIFICATION RECORD

January 16, 2006 (Version 1.0 template) INITIAL RELEASE, TO LOGO TF MOI GROUP

Andy Baldman: Initial Release

February 7, 2006 (Version 0.8) INITIAL RELEASE, TO LOGO TF MOI GROUP

Bryan Kantack: Initial Release

February 20, 2006 (Version 0.9)

Bryan Kantack: Updates made to reflect IW Event #1 Unified Test Document changes

March 17, 2006 (Version 0.91)

Bryan Kantack: General formatting, Update SATA templates to Rev 2.0 for all measurements

April 3, 2006 (Version 0.92)

Bryan Kantack: Removal of TX/RX test sections, incorporation of first-pass reviewer feedback

May 7, 2006 (Version 0.93)

Bryan Kantack: Update SATA templates to Rev 2.1 for all measurements; OOB timing updates for OOB-01 through OOB-07

May 25, 2006 (Version 0.94)

Bryan Kantack: General formatting and updates to align with Unified Test Document Rev 1.0RC2i (May 11, 2006); added

Unified Test Document section references to each measurement

June 8, 2006 (Version 0.95)

Bryan Kantack: Update to OOB-01 OOB Detection Threshold procedure (removed two unnecessary tests)

June 9, 2006 (Version 0.95RC) REVIEW RELEASE, TO LOGO TF MOI GROUP

Bryan Kantack: Release to LOGO TF MOI Group for final review and vote

June 19, 2006 (Version 0.96RC)

Bryan Kantack: Update TSG-01, TSG-02, TSG-09, TSG-10, PHY-02, PHY-04 text per reviewer feedback; changed COMAX

part number H303000202 to H303000204 to correctly reference new product revision; edited typographical

error in OOB-04 through OOB-07 test descriptions; incorporation of final reviewer feedback

June 21, 2006 (Version 1.0RC) REVIEW RELEASE, TO LOGO TF MOI GROUP

Bryan Kantack: Release to LOGO TF MOI Group for final review and vote

June 22, 2006 (Version 1.0RC2) REVIEW RELEASE, TO LOGO TF MOI GROUP

Bryan Kantack: Release to LOGO TF MOI Group for final review and vote; updated PHY-04 and TSG-02 text per committee

feedback

## **ACKNOWLEDGMENTS**

Agilent Technologies, Inc. would like to acknowledge the efforts of the following individuals in the development of this document.

SATA MOI Template Andrew Baldman University of New Hampshire Interoperability Lab

Creation David Woolf University of New Hampshire Interoperability Lab

Agilent PHY Test Bryan Kantack Agilent Technologies, Inc.

MOI Creation

Agilent Technologies, Inc. would like to acknowledge the efforts of the reviewers of this document.

Steven Wong, COMAX

Jeff Wolford, HP

Bent Hessen-Schmidt, SyntheSys Research

Yun Wang, ULINK Technology, Inc.

Andrew Baldman, University of New Hampshire Interoperability Lab

#### INTRODUCTION

The tests contained in this document are organized in order to simplify the identification of information related to a test, and to facilitate in the actual testing process. Tests are separated into groups, primarily in order to reduce setup time in the lab environment, however the different groups typically also tend to focus on specific aspects of device functionality.

The test definitions themselves are intended to provide a high-level description of the motivation, resources, procedures, and methodologies specific to each test. Formally, each test description contains the following sections:

## **Purpose**

The purpose is a brief statement outlining what the test attempts to achieve. The test is written at the functional level.

#### References

This section specifies all reference material *external* to the test suite, including the specific subclauses references for the test in question, and any other references that might be helpful in understanding the test methodology and/or test results. External sources are always referenced by a bracketed number (e.g., [1]) when mentioned in the test description. Any other references in the test description that are not indicated in this manner refer to elements within the test suite document itself (e.g., "Appendix 6.A", or "Table 6.1.1-1")

## **Resource Requirements**

The requirements section specifies the test hardware and/or software needed to perform the test. This is generally expressed in terms of minimum requirements, however in some cases specific equipment manufacturer/model information may be provided.

#### **Last Modification**

This specifies the date of the last modification to this test.

#### **Discussion**

The discussion covers the assumptions made in the design or implementation of the test, as well as known limitations. Other items specific to the test are covered here as well.

## **Test Setup**

The setup section describes the initial configuration of the test environment. Small changes in the configuration should not be included here, and are generally covered in the test procedure section (next).

#### **Procedure**

The procedure section of the test description contains the systematic instructions for carrying out the test. It provides a cookbook approach to testing, and may be interspersed with observable results.

#### **Observable Results**

This section lists the specific observables that can be examined by the tester in order to verify that the DUT is operating properly. When multiple values for an observable are possible, this section provides a short discussion on how to interpret them. The determination of a pass or fail outcome for a particular test is generally based on the successful (or unsuccessful) detection of a specific observable.

#### **Possible Problems**

This section contains a description of known issues with the test procedure, which may affect test results in certain situations. It may also refer the reader to test suite appendices and/or other external sources that may provide more detail regarding these issues.

# **GROUP 1: PHY GENERAL REQUIREMENTS**

## Overview:

This group of tests verifies the Phy General Requirements, as defined in Section 2.11 of the Serial ATA Interoperability Unified Test Document, Revision 0.93 (which references the Serial ATA, Revision 2.5).

#### Test PHY-01 - Unit Interval

Purpose: To verify that the Unit Interval of the DUT TX signaling is within the conformance limits.

#### References:

- [1] SATA Standard, 7.2.1, Table 20 General Specifications

- [2] Ibid, 7.2.2.1.3 Unit Interval

- [3] Ibid, 7.4.11 SSC Profile

- [4] SATA Interoperability Program Unified Test Document, 2.10.1 Unit Interval

#### **Resource Requirements:**

Agilent DSO81204A/B (12GHz bandwidth, 40GS/s per channel on 2 channels) with Agilent N5411A SATA Electrical Performance Validation and Compliance Test Software COMAX iSATA(cable connector) to SMA(f) test fixture distributed by CRUZ Systems (H303000204) Gen2i capable host PC running ULink, any other mechanism that makes the device produce the required patterns is acceptable.

See appendix A for details.

Last Template Modification: May 7, 2006 (Version 2.01)

#### **Discussion:**

Reference [1] specifies the general PHY conformance limits for SATA devices. This specification includes conformance limits for the mean Unit Interval (UI). Reference [2] provides the definition of this term for the purposes of SATA testing. Reference [3] defines the measurement requirements for this test.

In this test, the mean UI value is measured based on the average of at least 100,000 observed UI's, measured at the transmitter output.

The mean UI is measured from a Unit Interval measurement trend, and applies to signaling with SSC enabled and/or disabled. This value includes the long term frequency accuracy and the Spread Spectrum Clock FM frequency deviation. Tui max and Tui min are also measured.

#### **Test Setup:**

The N5411A automated test software will prompt you to make the device produce HFTP. When prompted, if you will use the ULink DriveMaster 2006 software to put the device into BIST, follow this procedure:

- 1) Connect a SATA cable from the host system's port 0 SATA connection to the device under test.

- 2) Launch DriveMaster 2006 on the host system and choose the 'Ctl SATA' Control Panel icon from DriveMaster's menu bar. The default SATA Phy Control port is port 0.

- 3) From the BIST method combo box, choose the appropriate supported BIST method for communicating with the drive. For the 80-bit Transmit only test option with ALIGN bypass and scramble bypass, choose T+S+A; for the far-end retimed loopback mode, choose L.

- 4) In the User Patterns combo box, choose the High-Transition Density Pattern (HTDP). This is implemented as the HFTP, or 4A4A4A4Ah 4A4A4Ah.

- 5) Click the 'BIST' button to initiate the BIST command script, and wait for the status in the lower left-hand corner of the SATA Control Panel dialog to update to BIST FIS SUCCEEDED. If the status reads BIST FIS FAILED, click the COMRESET radio button and repeat steps 3-5.

- 6) Disconnect the SATA cable from the device and plug in the H303000204 test fixture. The H303000204 is connected to channels 1 and 3 of the DSO81204A/B by two 36" SMA cables (Rosenberger or equivalent). OBSERVE the signal on the scope. If it is HFTP, press OK in the N5411A prompt. If not, the device did not properly handle BIST Activate FIS; a non-standard way to make it produce the desired pattern will be required.

#### **Test Procedure:**

This parameter is covered by Agilent Technologies, Inc. N5411A automated SATA compliance software, revision 2.01 or later. This is reported as Tui min and Tui max, with the appropriate limits. Either "PASS" or "FAIL" is shown for the unit interval test in the report generated at the completion of the testing. Both Min and Max tests must pass to pass the unit interval test.

#### **Observable Results:**

The mean Unit Interval value shall be between 666.4333 ps and 670.2333 ps for 1.5Gb/s devices, and between 333.2167ps and 335.1167ps for 3.0Gb/s devices.

#### Test PHY-02 - Frequency Long Term Stability

**Purpose:** To verify that the long term frequency stability of the DUT's transmitter is within the conformance limit.

#### References:

- [1] SATA Standard, 7.2.1, Table 20 General Specifications

- [2] Ibid, 7.2.2.1.4 TX Frequency Long Term Stability

- [3] Ibid, 7.4.6 Long Term Frequency Accuracy

- [4] SATA Interoperability Program Unified Test Document, 2.10.2 Frequency Long-Term Stability

#### **Resource Requirements:**

Same requirements as for PHY-01

**Last Template Modification:** May 7, 2006 (Version 2.01)

#### **Discussion:**

Reference [1] specifies the general PHY conformance limits for SATA devices. This specification includes conformance limits for the TX Frequency Long Term Stability. Reference [2] provides the definition of this term for the purposes of SATA testing. Reference [3] defines the measurement requirements for this test.

#### **Test Setup:**

Same setup as for PHY-01. There is no setup change for PHY-02.

#### **Test Procedure:**

This parameter is covered by Agilent Technologies, Inc. N5411A automated SATA compliance software, revision 2.01 or later. This is reported as a ppm error value with respect to the nominal data rate. Either "PASS" or "FAIL" is shown for the frequency long-term stability test in the report generated at the completion of the testing. For non-SSC enabled devices, both Min and Max tests must pass to pass the frequency long-term stability test. For SSC enabled devices, only the Max test must pass to pass the frequency long-term stability test.

The measurement for frequency long-term stability records both the min and max unit interval values after the 1.98MHz filter is applied. The ppm deviation is computed from the following operations and the worst case reported for pass/fail:

```

Max Test: ((Measured Max – Nominal)/Nominal)*1E6 < +350 ppm for pass Min Test: ((Measured Min – Nominal)/Nominal)* 1E6 < -350 ppm for pass

```

#### **Observable Results:**

The Frequency Long Term Stability value shall be between +/- 350ppm for both 1.5Gb/s and 3.0Gb/s devices.

#### Test PHY-03 - Spread-Spectrum Modulation Frequency

**Purpose:** To verify that the Spread Spectrum Modulation Frequency of the DUT's transmitter is within the conformance limits.

#### **References:**

- [1] SATA Standard, 7.2.1, Table 20 General Specifications

- [2] Ibid, 7.2.2.1.5 Spread-Spectrum Modulation Frequency

- [3] Ibid, 7.4.11 SSC Profile

- [4] SATA Interoperability Program Unified Test Document, 2.10.3 Spread-Spectrum Modulation Frequency

#### **Resource Requirements:**

Same requirements as for PHY-01

**Last Template Modification:** May 7, 2006 (Version 2.01)

#### **Discussion:**

Reference [1] specifies the general PHY conformance limits for SATA devices. This specification includes conformance limits for the Spread-Spectrum Modulation Frequency. Reference [2] provides the definition of this term for the purposes of SATA testing. Reference [3] defines the measurement requirements for this test.

In this test, the Spread-Spectrum Modulation Frequency,  $f_{SSC}$ , is measured, based on at least 10 complete SSC cycles.

Agilent's N5411A automated SATA compliance software will command the DSO81204B to acquire 2.05MSamples of data at 40GSa/s, or 51.25us of data, which is over 1.5 cycles of the slowest allowed SSC profile frequency at a repeating rate of 30kHz. The DSO81204B will then make 10 acquisitions to acquire a minimum of 15 SSC cycles, which provides sufficient data to analyze the Mean SSC frequency and downspread accuracy.

#### **Test Setup:**

Same setup as for PHY-01. There is no setup change for PHY-03, except that a 1.98MHz low-pass filter (LPF) is applied to the Unit Interval trend to intentionally remove high frequency jitter from the SSC measurement. Reference [1] requires that a LPF with a cutoff frequency of 60 times the 30kHz to 33kHz SSC modulation frequency be applied to the Unit Interval trend for the SSC measurement, which yields a LPF cutoff frequency of 1.8MHz to 1.98MHz. Since 33kHz is an acceptable SSC modulation frequency, the 1.98MHz LPF cutoff frequency at -3dB is used for all DUTs.

#### **Test Procedure:**

This parameter is covered by Agilent Technologies, Inc. N5411A automated SATA compliance software, revision 2.01 or later. The Mean frequency is measured at the 50% threshold of the Unit Interval trend and reported. The Mean is cumulative over all 10 acquisitions and the final Mean SSC modulation frequency is reported as the final value. Either "PASS" or "FAIL" is shown for the SSC frequency test in the report generated at the completion of the testing.

#### **Observable Results:**

The Spread-Spectrum Modulation Frequency value shall be between 30 kHz and 33 kHz for both 1.5Gb/s and 3.0Gb/s devices.

#### Test PHY-04 - Spread-Spectrum Modulation Deviation

**Purpose:** To verify that the Spread-Spectrum Modulation Deviation of the DUT's transmitter is within the conformance limits.

#### References:

- [1] SATA Standard, 7.2.1, Table 20 General Specifications

- [2] Ibid, 7.2.2.1.6 Spread-Spectrum Modulation Deviation

- [3] Ibid, 7.4.11 SSC Profile

- [4] SATA Interoperability Program Unified Test Document, 2.10.4 Spread-Spectrum Modulation Deviation

#### **Resource Requirements:**

Same requirements as for PHY-01

**Last Template Modification:** May 7, 2006 (Version 2.01)

#### **Discussion:**

Reference [1] specifies the general PHY conformance limits for SATA devices. This specification includes conformance limits for the Spread-Spectrum Modulation Deviation. Reference [2] provides the definition of this term for the purposes of SATA testing. Reference [3] defines the measurement requirements for this test.

In this test, the Spread-Spectrum Modulation Frequency,  $f_{SSC}$ , is measured, based on at least 10 complete SSC cycles.

Agilent's N5411A automated SATA compliance software will command the DSO81204B to acquire 2.05MSamples of data at 40GSa/s, or 51.25us of data, which is over 1.5 cycles of the slowest allowed SSC profile frequency at a repeating rate of 30kHz. The DSO81204B will then make 10 acquisitions to acquire a minimum of 15 SSC cycles, which provides sufficient data to analyze the SSC frequency and downspread accuracy.

Note that Tui min limit includes 350ppm tolerance above 0ppm and Tui max limit includes 350ppm tolerance below -5000ppm but the modulation deviation calculation does not include those tolerances since a 1.98MHz LPF is being applied to the Unit Interval measurement trend, intentionally excluding high-frequency jitter from the SSC measurement.

#### **Test Setup:**

Same setup as for PHY-01. There is no setup change for PHY-04, except that a 1.98MHz low-pass filter (LPF) is applied to the Unit Interval trend to intentionally remove high frequency jitter from the SSC measurement. Reference [1] requires that a LPF with a cutoff frequency of 60 times the 30kHz to 33kHz SSC modulation frequency be applied to the Unit Interval trend for the SSC measurement, which yields a LPF cutoff frequency of 1.8MHz to 1.98MHz. Since 33kHz is an acceptable SSC modulation frequency, the 1.98MHz LPF cutoff frequency at -3dB is used for all DUTs.

#### **Test Procedure:**

This parameter is covered by Agilent Technologies, Inc. N5411A automated SATA compliance software, revision 2.01 or later. The Min and Max Unit Interval is measured over the entire trend and converted to ppm deviation. The Mean is cumulative over all 10 acquisitions and the final Min and Max SSC modulation deviation reported as the final value. Either "PASS" or "FAIL" is shown for the SSC modulation deviation test in the report generated at the completion of the testing.

The measurement for SSC modulation deviation records both the min and max unit interval values after the 1.98MHz filter is applied. The ppm deviation is computed from the following operations and the worst case reported for pass/fail:

Min Test: ((Measured Min – Nominal)/Nominal)\*1E6 < -5000 ppm for pass

#### **Observable Results:**

The Spread-Spectrum Modulation Deviation value shall be above -5000 ppm for both 1.5Gb/s and 3.0Gb/s devices

#### **Possible Problems:**

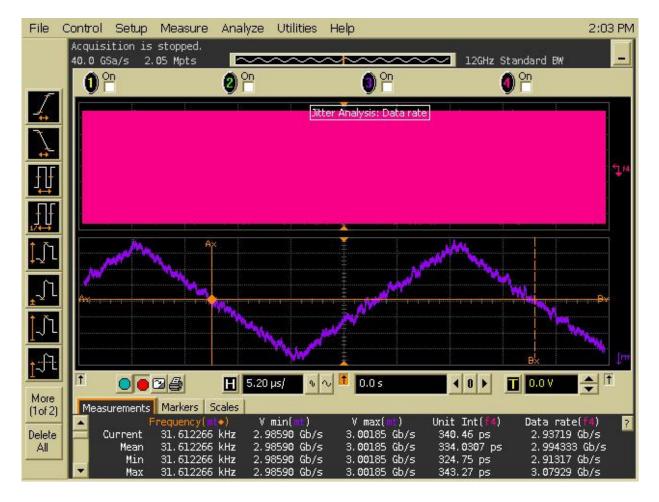

We have seen many devices that have less than 5000ppm of modulation deviation (frequency downspread), but that are 'shifted' such that the maximum data rate on the bus (minimum UI) is faster than the allowed ppm deviation. The upper limit of the SSC modulation deviation test is 0ppm, and does not include the +/-350ppm limits allowed for long-term stability over the entire modulation frequency range of the active link. Comparison tests have been conducted between the oscilloscope measurement trend method and a spectrum analyzer to determine the differences observed between the two measurement methods. Generally, spectrum analyzers will have additional sideband information that is ignored in traditional readings, and may report lower ppm deviation tolerances than the oscilloscope filtered Unit Interval trend method. The example SSC test from an Agilent DSO81204B below shows a device with a Data Rate (inverse of Unit Interval) that is +616ppm fast per the specification. An Agilent 8565E 50GHz spectrum analyzer with a RBW of 10kHz, sweep rate of 8 seconds and span of 15MHz reported +100ppm on the same DUT.

# **GROUP 2: PHY TRANSMITTED SIGNAL REQUIREMENTS**

## **Overview:**

This group of tests verifies the Phy Transmitted Signal Requirements, as defined in Section 2.13 of the SATA Interoperability Unified Test Document, v0.9 (which references the SATA Standard, v2.5).

#### Test TSG-01 - Differential Output Voltage

Purpose: To verify that the Differential Output Voltage of the DUT's transmitter is within the conformance limits.

#### References:

- [1] SATA Standard, 7.2.1, Table 22 Transmitted Signal Requirements

- [2] Ibid, 7.2.2.3.1 TX Differential Output Voltage

- [3] Ibid, 7.4.4 Transmitter Amplitude

- [4] SATA Interoperability Program Unified Test Document, 2.12.1 Differential Output Voltage

#### **Resource Requirements:**

Same as for PHY-01, repeated here for convenience:

Agilent DSO81204A/B (12GHz bandwidth, 40GS/s per channel on 2 channels) with Agilent N5411A SATA Electrical Performance Validation and Compliance Test Software COMAX iSATA(cable connector) to SMA(f) test fixture distributed by CRUZ Systems (H303000204) Gen2i capable host PC running ULink, any other mechanism that makes the device produce the required patterns is acceptable.

See appendix A for details.

Last Template Modification: May 7, 2006 (Version 2.01)

#### Discussion:

Reference [1] specifies the Transmitted Signal conformance limits for SATA devices. This specification includes conformance limits for the Differential Output Voltage. Reference [2] provides the definition of this term for the purposes of SATA testing. Reference [3] defines the measurement requirements for this test.

Vdiff Min is tested with HFTP, MFTP and LBP. Vdiff Max is tested with MFTP and LFTP.

Note that LBP depends on the Running Disparity, which cannot be known. See possible problems, below.

#### **Test Setup:**

Since PHY-01 the device has been producing HFTP and it is already connected to the scope. The N5411A SATA compliance software will prompt for MFTP and LFTP when it needs those patterns. When prompted for MFTP, if you will use the ULink DriveMaster 2006 software to put the device into BIST, follow this procedure:

- 1) Connect a SATA cable from the host system's port 0 SATA connection to the device under test.

- Launch DriveMaster 2006 on the host system and choose the 'Ctl SATA' Control Panel icon from DriveMaster's menu bar. The default SATA Phy Control port is port 0.

- 3) From the BIST method combo box, choose the appropriate supported BIST method for communicating with the drive. For the 80-bit Transmit only test option with ALIGN bypass and scramble bypass, choose T+S+A; for the far-end retimed loopback mode, choose L.

- 4) In the User Patterns combo box, choose the User Patterns selection. Now enter 78787878h 78787878h into the 64-bit Data (Hex) boxes just above the User Patterns combo box. This will encode as a repeating D24.3 on the line and provide a half-rate clock-like data pattern (1100110011).

- 5) Click the 'BIST' button to initiate the BIST command script, and wait for the status in the lower left-hand corner of the SATA Control Panel dialog to update to BIST FIS SUCCEEDED. If the status reads BIST FIS FAILED, click the COMRESET radio button and repeat steps 3-5.

- 6) Disconnect the SATA cable from the device and plug in the H303000204 test fixture. The H303000204 is connected to channels 1 and 3 of the DSO81204A/B by two 36" SMA cables (Rosenberger or equivalent). OBSERVE the signal on the scope. If it is correct, press OK in the N5411A prompt. If not, the device did not properly handle BIST Activate FIS; a non-standard way to make it produce the desired pattern will be required.

15

When prompted for LBP, if you will use the ULink DriveMaster 2006 software to put the device into BIST, follow this procedure:

- 1) Connect a SATA cable from the host system's port 0 SATA connection to the device under test.

- 2) Launch DriveMaster 2006 on the host system and choose the 'Ctl SATA' Control Panel icon from DriveMaster's menu bar. The default SATA Phy Control port is port 0.

- 3) From the BIST method combo box, choose the appropriate supported BIST method for communicating with the drive. For the 80-bit Transmit only test option with ALIGN bypass and scramble bypass, choose T+S+A; for the far-end retimed loopback mode, choose L.

- 4) In the User Patterns combo box, choose the Lone-Bit Pattern (+ve) selection. This is implemented as 8BFC8DFCh 8EFC8BFCh.

- 5) Click the 'BIST' button to initiate the BIST command script, and wait for the status in the lower left-hand corner of the SATA Control Panel dialog to update to BIST FIS SUCCEEDED. If the status reads BIST FIS FAILED, click the COMRESET radio button and repeat steps 3-5.

- 6) Disconnect the SATA cable from the device and plug in the H303000204 test fixture. The H303000204 is connected to channels 1 and 3 of the DSO81204A/B by two 36" SMA cables (Rosenberger or equivalent). OBSERVE the signal on the scope. If it is LBP, press OK in the N5411A prompt. If not, the device did not properly handle BIST Activate FIS; a non-standard way to make it produce the desired pattern will be required.

#### **Test Procedure:**

This parameter is covered by Agilent Technologies, Inc. N5411A automated SATA compliance software, revision 2.01 or later. Interim values for UH (HFTP upper), LH (HFTP lower), UM (MFTP upper), LM (MFTP lower), DHM (worst-case differential HFTP or differential MFTP), A (LBP lone 1-bit upper) and B (LBP lone 0-bit lower) are measured and computed to determine the final Vtest value for the Minimum Amplitude test. These interim values and screen captures can also be a helpful aid in debugging which pattern, and specifically, which bit failed the test. Similar steps are used to setup the MFTP and LFTP patterns used for the Maximum Amplitude test.

NOTE: The N5411A maximum amplitude test does not test physical voltage, but instead, the ratio of amplitude histogram points at or above the physical specification limit compared to total amplitude histogram points at or above +/- DOV/2. Again, pu, nu, NU, pl, nl and NL are reported out to assist in debug. This methodology is provided per the VdiffTX, Max measurement definition in reference [1]. Either "PASS" or "FAIL" is shown for the minimum amplitude test in the report generated at the completion of the testing.

Reference [4] addresses the measurement of VdiffTX, Min and VdiffTX, Max per the SATA-IO LOGO IW testing requirements as follows:

```

DOV Min = Vtest(min) = min(DH, DM, VtestLBP)

DOV Max = Vtest(max) = max(DH, DM, VtestLBP)

```

#### **Observable Results:**

The Differential Output Voltage shall be between the limits specified in reference [4]. For convenience, the values are reproduced below. For the differential amplitude voltage test to pass, the following two conditions must both be met: 1) The minimum differential amplitude value, Vtest(min), must meet the DOV minimum test limits, 2) the maximum differential amplitude value, Vtest(max), must meet the DOV maximum test limits.

| Device Type | DOV Min | DOV Max |

|-------------|---------|---------|

| Gen1i       | 400 mV  | 800 mV  |

| Gen2i       | 400 mV  | 800 mV  |

#### **Possible Problems:**

The SATA specification includes a pattern that makes LBP for RD+, and another if RD-. Since RD is not known, with either one there is a 50% chance that LBP will actually be produced correctly on the line. ULink's DriveMaster program provides both +ve and -ve versions of the LBP to ensure that this test can be performed correctly per the specification. The Agilent N5411A SATA compliance software will wait for the scope to trigger on and identify the 4-1-3 lone-bit pattern prior to performing the test. If the lone-bit cannot be identified, the N5411A will prompt you to try a different pattern. Return to the Test Setup section of this measurement and repeat steps 4 and 5, using the Lone-Bit Pattern (-ve) selection in the ULink DriveMaster software instead. After 2-3 BIST enable attempts with each pattern, you should be able to complete the Minimum Amplitude test. If not, a non-standard way to enable the Lone-Bit Pattern will be required.

#### Test TSG-02 - Rise/Fall Time

Purpose: To verify that the Rise/Fall time of the DUT's transmitter is within the conformance limits.

#### References

- [1] SATA Standard, 7.2.1, Table 22 Transmitted Signal Requirements

- [2] Ibid, 7.2.2.3.3 TX Rise/Fall Time

- [3] Ibid, 7.4.3 Rise and Fall Times

- [4] SATA Interoperability Program Unified Test Document, 2.12.2 Rise/Fall Time

#### **Resource Requirements:**

Same as for TSG-01.

See appendix A for details.

Last Template Modification: May 7, 2006 (Version 2.01)

#### Discussion:

Reference [1] specifies the Transmitted Signal conformance limits for SATA devices. This specification includes conformance limits for the Rise/Fall Time. Reference [2] provides the definition of this term for the purposes of SATA testing. Reference [3] defines the measurement requirements for this test.

TSG-02 is tested using HFTP.

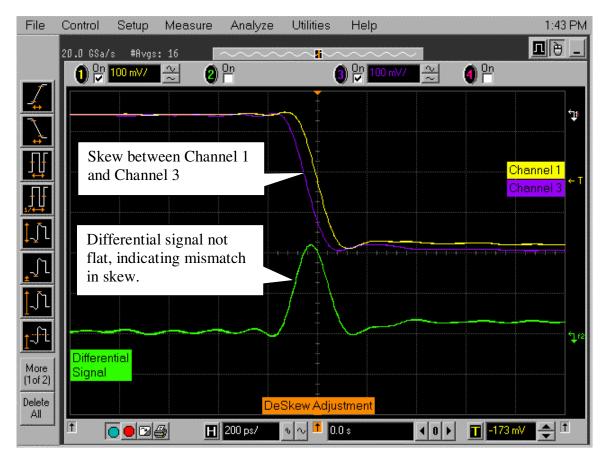

The cables connecting the COMAX SATA TEST FIXTURE DISTRIBUTED BY CRUZ SYSTEMS (H303000204) to the scope must be deskewed, as discussed in Appendix A. Skew lengthens the measured differential rise and fall times.

#### **Test Setup:**

The N5411A SATA compliance software will prompt for HFTP when it needs that patterns. When prompted for HFTP, if you will use the ULink DriveMaster 2006 software to put the device into BIST, follow this procedure:

- 1) Connect a SATA cable from the host system's port 0 SATA connection to the device under test.

- 2) Launch DriveMaster 2006 on the host system and choose the 'Ctl SATA' Control Panel icon from DriveMaster's menu bar. The default SATA Phy Control port is port 0.

- 3) From the BIST method combo box, choose the appropriate supported BIST method for communicating with the drive. For the 80-bit Transmit only test option with ALIGN bypass and scramble bypass, choose T+S+A; for the far-end retimed loopback mode, choose L.

- 4) For HFTP: In the User Patterns combo box, choose the High-Transition Density Pattern (HTDP). This is implemented as the HFTP, or 4A4A4A4A4 4A4A4Ah.

- 5) Click the 'BIST' button to initiate the BIST command script, and wait for the status in the lower left-hand corner of the SATA Control Panel dialog to update to BIST FIS SUCCEEDED. If the status reads BIST FIS FAILED, click the COMRESET radio button and repeat steps 3-5.

- 6) Disconnect the SATA cable from the device and plug in the H303000204 test fixture. The H303000204 is connected to channels 1 and 3 of the DSO81204A/B by two 36" SMA cables (Rosenberger or equivalent). OBSERVE the signal on the scope. If it is correct, press OK in the N5411A prompt. If not, the device did not properly handle BIST Activate FIS; a non-standard way to make it produce the desired pattern will be required.

#### **Test Procedure:**

This parameter is covered by Agilent Technologies, Inc. N5411A automated SATA compliance software, revision 2.01 or later. The Min, Max and Mean Rise and Fall Times are measured over the entire data

acquisition (about 38,000 rising and 38,000 falling edges per acquisition). The Mean value is reported as the final value and compared only to the RFT Max value in the table below for pass/fail. Either "PASS" or "FAIL" is shown for the Rise/Fall time test in the report generated at the completion of the testing.

#### **Observable Results:**

The Mean TX Rise/Fall Times shall be between the limits specified in reference [1]. For convenience, the values are reproduced below. Note: Failures at minimum rate have not been shown to affect interoperability and will not be included in determining pass/fail for Interoperability testing.

| Device Type | RFT Min | RFT Max |

|-------------|---------|---------|

| Gen1i       | 100 ps  | 273 ps  |

| Gen2i       | 67 ps   | 136 ps  |

#### Test TSG-03 - Differential Skew

Purpose: To verify that the Differential Skew of the DUT's transmitter is within the conformance limits.

#### References:

- [1] SATA Standard, 7.2.1, Table 22 Transmitted Signal Requirements

- [2] Ibid, 7.2.2.3.4 TX Differential Skew (Gen2i, Gen1x, Gen2x)

- [3] Ibid, 7.4.12 Intra-pair Skew

- [4] SATA Interoperability Program Unified Test Document, 2.12.3 Differential Skew

#### **Resource Requirements:**

Same as for TSG-01.

See appendix A for details.

Last Template Modification: May 7, 2006 (Version 2.01)

### Discussion:

Reference [1] specifies the Transmitted Signal conformance limits for SATA devices. This specification includes conformance limits for Differential Skew. Reference [2] provides the definition of this term for the purposes of SATA testing. Reference [3] defines the measurement requirements for this test.

Skew is measured with HFTP and MFTP.

The cables connecting the COMAX SATA TEST FIXTURE DISTRIBUTED BY CRUZ SYSTEMS (H303000204) to the scope must be deskewed, as discussed in Appendix A. Uncompensated cable skew contributes directly to measured differential skew.

#### **Test Setup:**

The N5411A SATA compliance software will prompt for HFTP and MFTP when it needs those patterns. When prompted for HFTP or MFTP, if you will use the ULink DriveMaster 2006 software to put the device into BIST, follow this procedure:

- 1) Connect a SATA cable from the host system's port 0 SATA connection to the device under test.

- 2) Launch DriveMaster 2006 on the host system and choose the 'Ctl SATA' Control Panel icon from DriveMaster's menu bar. The default SATA Phy Control port is port 0.

- 3) From the BIST method combo box, choose the appropriate supported BIST method for communicating with the drive. For the 80-bit Transmit only test option with ALIGN bypass and scramble bypass, choose T+S+A; for the far-end retimed loopback mode, choose L.

- 4) For HFTP: In the User Patterns combo box, choose the High-Transition Density Pattern (HTDP). This is implemented as the HFTP, or 4A4A4A4A4 4A4A4A4A. For MFTP: In the User Patterns combo box, choose the User Patterns selection. Now enter 78787878h 78787878h into the 64-bit Data (Hex) boxes just above the User Patterns combo box. This will encode as a repeating D24.3 on the line and provide a half-rate clock-like data pattern (1100110011).

- 5) Click the 'BIST' button to initiate the BIST command script, and wait for the status in the lower left-hand corner of the SATA Control Panel dialog to update to BIST FIS SUCCEEDED. If the status reads BIST FIS FAILED, click the COMRESET radio button and repeat steps 3-5.

- 6) Disconnect the SATA cable from the device and plug in the H303000204 test fixture. The H303000204 is connected to channels 1 and 3 of the DSO81204A/B by two 36" SMA cables (Rosenberger or equivalent). OBSERVE the signal on the scope. If it is correct, press OK in the N5411A prompt. If not, the device did not properly handle BIST Activate FIS; a non-standard way to make it produce the desired pattern will be required.

#### **Test Procedure:**

This parameter is covered by Agilent Technologies, Inc. N5411A automated SATA compliance software, revision 2.01 or later. Differential skew is measured as the difference between the mean of the rising edge in a single-ended eye diagrams of TX+ and the mean of the falling edge in a single-ended eye diagram of TX-, repeat the measurement this time measuring the difference between the mean of the rising edge in a single-ended eye diagrams of TX- and the mean of the falling edge in a single-ended eye diagram of TX+, finally compute the Differential Skew = average of the magnitude (absolute value) of the two mean skews. This removes the effect of rise-fall imbalance from the skew measurement in accordance with section 7.4.12 of the Serial ATA revision 2.5. Two differential skew values are provided, one for HFTP and one for MFTP, and both must meet the Max Diff Skew requirements in reference [1], which are repeated in the table below for convenience. Either "PASS" or "FAIL" is shown for the differential skew test in the report generated at the completion of the testing.

#### **Observable Results:**

The TX Differential Skew shall be between the limits specified in reference [1]. For convenience, the values are reproduced below.

| Device Type | Max Diff Skew |

|-------------|---------------|

| Gen1i       | 20 ps         |

| Gen2i       | 20 ps         |

#### Test TSG-04 - AC Common Mode Voltage

Purpose: To verify that the AC Common Mode Voltage of the DUT's transmitter is within the conformance limits.

#### References:

- [1] SATA Standard, 7.2.1, Table 22 Transmitted Signal Requirements

- [2] Ibid, 7.2.2.3.5 TX AC Common Mode Voltage (Gen2i, Gen1x, Gen2x)

- [3] Ibid, 7.4.17 TX AC Common Mode Voltage

- [4] SATA Interoperability Program Unified Test Document, 2.12.4 AC Common Mode Voltage

#### **Resource Requirements:**

Same as for TSG-01.

See appendix A for details.

Last Template Modification: May 7, 2006 (Version 2.01)

## Discussion:

Reference [1] specifies the Transmitted Signal conformance limits for SATA devices. This specification includes conformance limits for the TX AC Common Mode Voltage. Reference [2] provides the definition of this term for the purposes of SATA testing. Reference [3] defines the measurement requirements for this test.

TSG-04 is tested with MFTP.

The cables connecting the COMAX SATA TEST FIXTURE DISTRIBUTED BY CRUZ SYSTEMS (H303000204) to the scope must be deskewed, as discussed in Appendix A. Skew contributes directly to common mode spikes which if large enough, even though they are low pass filtered to half the bit rate, can cause failure.

#### **Test Setup:**

The N5411A SATA compliance software will prompt for MFTP. When prompted for MFTP, if you will use the ULink DriveMaster 2006 software to put the device into BIST, follow this procedure:

- 1) Connect a SATA cable from the host system's port 0 SATA connection to the device under test.

- 2) Launch DriveMaster 2006 on the host system and choose the 'Ctl SATA' Control Panel icon from DriveMaster's menu bar. The default SATA Phy Control port is port 0.

- 3) From the BIST method combo box, choose the appropriate supported BIST method for communicating with the drive. For the 80-bit Transmit only test option with ALIGN bypass and scramble bypass, choose T+S+A; for the far-end retimed loopback mode, choose L.

- 4) In the User Patterns combo box, choose the User Patterns selection. Now enter 78787878h 78787878h into the 64-bit Data (Hex) boxes just above the User Patterns combo box. This will encode as a repeating D24.3 on the line and provide a half-rate clock-like data pattern (1100110011).

- 5) Click the 'BIST' button to initiate the BIST command script, and wait for the status in the lower left-hand corner of the SATA Control Panel dialog to update to BIST FIS SUCCEEDED. If the status reads BIST FIS FAILED, click the COMRESET radio button and repeat steps 3-5.

- 6) Disconnect the SATA cable from the device and plug in the H303000204 test fixture. The H303000204 is connected to channels 1 and 3 of the DSO81204A/B by two 36" SMA cables (Rosenberger or equivalent). OBSERVE the signal on the scope. If it is correct, press OK in the N5411A prompt. If not, the device did not properly handle BIST Activate FIS; a non-standard way to make it produce the desired pattern will be required.

#### **Test Procedure:**

This parameter is covered by Agilent Technologies, Inc. N5411A automated SATA compliance software, revision 2.01 or later. The test is performed as (TX++TX-)/2, low-pass filter applied with a -3dB cutoff frequency of bit-rate/2 and peak-peak amplitude of the filter output measured as the final AC common mode voltage value. Either "PASS" or "FAIL" is shown for the common mode voltage test in the report generated at the completion of the testing.

#### **Observable Results:**

The AC Common Mode Voltage value shall be less than 50 mVp-p for Gen2i and Gen2m devices.

#### Test TSG-05 - Rise/Fall Imbalance

Purpose: To verify that the Rise/Fall Imbalance of the DUT's transmitter is within the conformance limits.

#### References:

- [1] SATA Standard, 7.2.1, Table 22 Transmitted Signal Requirements

- [2] Ibid, 7.2.2.3.9 TX Rise/Fall Imbalance

- [3] Ibid, 7.4.16 TX Rise/Fall Imbalance

- [4] SATA Interoperability Program Unified Test Document, 2.12.5 Rise/Fall Imbalance

## **Resource Requirements:**

Same as for TSG-01.

See appendix A for details.

Last Template Modification: May 7, 2006 (Version 2.01)

#### **Discussion:**

Reference [1] specifies the Transmitted Signal conformance limits for SATA devices. This specification includes conformance limits for the Rise/Fall Imbalance. Reference [2] provides the definition of this term for the purposes of SATA testing. Reference [3] defines the measurement requirements for this test.

Rise/Fall imbalance is measured with HFTP and MFTP. References [2] and [3] both define two values to be computed, for each pattern. The two values compare TX+ rise to TX- fall, and TX- rise to TX+ fall. The results are expressed as a percentage of the average of the two items being compared.

#### **Test Setup:**

The N5411A SATA compliance software will prompt for HFTP and MFTP when it needs those patterns. When prompted for HFTP or MFTP, if you will use the ULink DriveMaster 2006 software to put the device into BIST, follow this procedure:

- 1) Connect a SATA cable from the host system's port 0 SATA connection to the device under test.

- 2) Launch DriveMaster 2006 on the host system and choose the 'Ctl SATA' Control Panel icon from DriveMaster's menu bar. The default SATA Phy Control port is port 0.

- 3) From the BIST method combo box, choose the appropriate supported BIST method for communicating with the drive. For the 80-bit Transmit only test option with ALIGN bypass and scramble bypass, choose T+S+A; for the far-end retimed loopback mode, choose L.

- 4) For HFTP: In the User Patterns combo box, choose the High-Transition Density Pattern (HTDP). This is implemented as the HFTP, or 4A4A4A4A4 4A4A4A4Ah. For MFTP: In the User Patterns combo box, choose the User Patterns selection. Now enter 78787878 78787878 into the 64-bit Data (Hex) boxes just above the User Patterns combo box. This will encode as a repeating D24.3 on the line and provide a half-rate clock-like data pattern (1100110011).

- 5) Click the 'BIST' button to initiate the BIST command script, and wait for the status in the lower left-hand corner of the SATA Control Panel dialog to update to BIST FIS SUCCEEDED. If the status reads BIST FIS FAILED, click the COMRESET radio button and repeat steps 3-5.

- 6) Disconnect the SATA cable from the device and plug in the H303000204 test fixture. The H303000204 is connected to channels 1 and 3 of the DSO81204A/B by two 36" SMA cables (Rosenberger or equivalent). OBSERVE the signal on the scope. If it is correct, press OK in the N5411A prompt. If not, the device did not properly handle BIST Activate FIS; a non-standard way to make it produce the desired pattern will be required.

#### **Test Procedure:**

This parameter is covered by Agilent Technologies, Inc. N5411A automated SATA compliance software, revision 2.01 or later. Either "PASS" or "FAIL" is shown for the rise/fall imbalance test in the report generated at the completion of the testing.

#### **Observable Results:**

The Rise/Fall Imbalance value shall be less than 20% for Gen2i and Gen2m devices.

## Test TSG-06 - Amplitude Imbalance

**Purpose:** To verify that the Amplitude Imbalance of the DUT's transmitter is within the conformance limits.

#### References:

- [1] SATA Standard, 7.2.1, Table 22 Transmitted Signal Requirements

- [2] Ibid, 7.2.2.3.10 TX Amplitude Imbalance (Gen2i, Gen1x, Gen2x)

- [3] Ibid, 7.4.15 TX Amplitude Imbalance

- [4] SATA Interoperability Program Unified Test Document, 2.12.6 Amplitude Imbalance

#### **Resource Requirements:**

Same as for TSG-01.

See appendix A for details.

**Last Template Modification:** May 7, 2006 (Version 2.01)

## Discussion:

Reference [1] specifies the Transmitted Signal conformance limits for SATA devices. This specification includes conformance limits for the TX Amplitude Imbalance. Reference [2] provides the definition of this term for the purposes of SATA testing. Reference [3] defines the measurement requirements for this test.

Amplitude Imbalance is measured with HFTP and MFTP.

This parameter is a measure of the match in the single-ended amplitudes of the TX+ and TXsignals. The test setup shown Figure 109 shall be used for this measurement. This parameter shall be measured and met with both the HFTP and MFTP patterns. Clock-like patterns are used here to enable the use of standard mode-based amplitude measurements for the sole purpose of determining imbalance. The measurement of differential amplitude uses a different method. In order to determine the amplitude imbalance, single ended mode high and mode low based amplitudes of both TX+ and TX- over 10 to 20 cycles of the clock-like pattern being used shall be determined. The amplitude imbalance value for that pattern is then determined by the equation:

absolute value(TX+ amplitude - TX- amplitude)/average where average is (TX+ amplitude + TX- amplitude)/2

#### **Test Setup:**

The N5411A SATA compliance software will prompt for HFTP and MFTP when it needs those patterns. When prompted for HFTP or MFTP, if you will use the ULink DriveMaster 2006 software to put the device into BIST, follow this procedure:

- 1) Connect a SATA cable from the host system's port 0 SATA connection to the device under test.

- 2) Launch DriveMaster 2006 on the host system and choose the 'Ctl SATA' Control Panel icon from DriveMaster's menu bar. The default SATA Phy Control port is port 0.

- 3) From the BIST method combo box, choose the appropriate supported BIST method for communicating with the drive. For the 80-bit Transmit only test option with ALIGN bypass and scramble bypass, choose T+S+A; for the far-end retimed loopback mode, choose L.

- 4) For HFTP: In the User Patterns combo box, choose the High-Transition Density Pattern (HTDP). This is implemented as the HFTP, or 4A4A4A4A4 4A4A4A4Ah. For MFTP: In the User Patterns combo box, choose the User Patterns selection. Now enter 78787878h 78787878h into the 64-bit Data (Hex) boxes just above the User Patterns combo box. This will encode as a repeating D24.3 on the line and provide a half-rate clock-like data pattern (1100110011).

- 5) Click the 'BIST' button to initiate the BIST command script, and wait for the status in the lower left-hand corner of the SATA Control Panel dialog to update to BIST FIS SUCCEEDED. If the status reads BIST FIS FAILED, click the COMRESET radio button and repeat steps 3-5.

- 6) Disconnect the SATA cable from the device and plug in the H303000204 test fixture. The H303000204 is connected to channels 1 and 3 of the DSO81204A/B by two 36" SMA cables

(Rosenberger or equivalent). OBSERVE the signal on the scope. If it is correct, press OK in the N5411A prompt. If not, the device did not properly handle BIST Activate FIS; a non-standard way to make it produce the desired pattern will be required.

#### **Test Procedure:**

This parameter is covered by Agilent Technologies, Inc. N5411A automated SATA compliance software, revision 2.01 or later. Either "PASS" or "FAIL" is shown for the rise/fall imbalance test in the report generated at the completion of the testing.

#### **Observable Results:**

The TX Amplitude Imbalance value shall be less than 10% for Gen1x, Gen2i, Gen2m, and Gen2x devices.

#### Test TSG-07 - TJ at Connector, Data, 5UI

Purpose: To verify that the TJ at Connector (Data, 5UI) of the DUT's transmitter is within the conformance limits.

#### References:

- [1] SATA Standard, 7.2.1, Table 22 Transmitted Signal Requirements

- [2] Ibid, 7.2.2.3.11

- [3] Ibid, 7.4.8

- [4] SATA Interoperability Program Unified Test Document, 2.12.7 TJ at Connector, Data, 5UI

#### **Resource Requirements:**

Same as for TSG-01.

See appendix A for details.

**Last Template Modification:** May 7, 2006 (Version 2.01)

## Discussion:

Reference [1] specifies the Transmitted Signal conformance limits for SATA devices. This specification includes conformance limits for the TJ at Connector (Data, 5UI). Reference [2] provides the definition of this term for the purposes of SATA testing. Reference [3] defines the measurement requirements for this test.

As noted directly in Reference [4], this test is **OPTIONAL** for all components. For components which support 3Gb/s, this requirement would be tested at 1.5Gb/s. For this test, the methodology of obtaining the result must follow a filtered TIE based method, similar to that for obtaining results for TSG-11 and TSG-12. In the past, an N-cycle method was used but is no longer preferred for the use of the interoperability testing.

For the Integrator's List test program jitter measurements are required to be made with HFTP and LBP, and if time permits should also be made with SSOP.

#### **Test Setup:**

The N5411A SATA compliance software will prompt for HFTP, LBP and/or SSOP when it needs those patterns. When prompted, if you will use the ULink DriveMaster 2006 software to put the device into BIST, follow this procedure:

- 1) Connect a SATA cable from the host system's port 0 SATA connection to the device under test.

- 2) Launch DriveMaster 2006 on the host system and choose the 'Ctl SATA' Control Panel icon from DriveMaster's menu bar. The default SATA Phy Control port is port 0.

- 3) From the BIST method combo box, choose the appropriate supported BIST method for communicating with the drive. For the 80-bit Transmit only test option with ALIGN bypass and scramble bypass, choose T+S+A; for the far-end retimed loopback mode, choose L.

- 4) For HFTP: In the User Patterns combo box, choose the High-Transition Density Pattern (HTDP). This is implemented as the HFTP, or 4A4A4A4A4 4A4A4A4A. Click the 'BIST' button to initiate the BIST command script, and wait for the status in the lower left-hand corner of the SATA Control Panel dialog to update to BIST FIS SUCCEEDED. If the status reads BIST FIS FAILED, click the COMRESET radio button and repeat steps 3-5.

- 5) Disconnect the SATA cable from the device and plug in the H303000204 test fixture. The H303000204 is connected to channels 1 and 3 of the DSO81204A/B by two 36" SMA cables (Rosenberger or equivalent). OBSERVE the signal on the scope. If it is correct, press OK in the N5411A prompt. If not, the device did not properly handle BIST Activate FIS; a non-standard way to make it produce the desired pattern will be required.

#### **Test Procedure:**

This parameter is covered by Agilent Technologies, Inc. N5411A automated SATA compliance software, revision 2.01 or later. Either "PASS" or "FAIL" is shown for the TJ at Connector, Data, 5UI test in the report generated at the completion of the testing.

#### **Observable Results:**

The TJ at Connector (Data, 5UI) value shall be less than 0.355 UI for Gen1i and Gen1m devices.

#### Possible Problems:

The SATA specification includes a pattern that makes LBP for RD+, and another if RD-. Since RD is not known, with either one there is a 50% chance that LBP will actually be produced correctly on the line. ULink's DriveMaster program provides both +ve and -ve versions of the LBP to ensure that this test can be performed correctly per the specification. The Agilent N5411A SATA compliance software will wait for the scope to trigger on and identify the 4-1-3 lone-bit pattern prior to performing the test. If the lone-bit cannot be identified, the N5411A will prompt you to try a different pattern. Return to the Test Setup section of this measurement and repeat steps 4 and 5, using the Lone-Bit Pattern (-ve) selection in the ULink DriveMaster software instead. After 2-3 BIST enable attempts with each pattern, you should be able to complete the Minimum Amplitude test. If not, a non-standard way to enable the Lone-Bit Pattern will be required.

#### Test TSG-08 - DJ at Connector, Data, 5UI

**Purpose:** To verify that the DJ at Connector (Data, 5UI) of the DUT's transmitter is within the conformance limits.

#### References:

- [1] SATA Standard, 7.2.1, Table 22 Transmitted Signal Requirements

- [2] Ibid, 7.2.2.3.11

- [3] Ibid, 7.4.8

- [4] SATA Interoperability Program Unified Test Document, 2.12.8 DJ at Connector, Data, 5UI

#### **Resource Requirements:**

Same as for TSG-01.

See appendix A for details.

**Last Template Modification:** May 7, 2006 (Version 2.01)

#### Discussion:

Reference [1] specifies the Transmitted Signal conformance limits for SATA devices. This specification includes conformance limits for the DJ at Connector (Data, 5UI). Reference [2] provides the definition of this term for the purposes of SATA testing. Reference [3] defines the measurement requirements for this test.

As noted directly in Reference [4], this test is **OPTIONAL** for all components. For components which support 3Gb/s, this requirement would be tested at 1.5Gb/s. For this test, the methodology of obtaining the result must follow a filtered TIE based method, similar to that for obtaining results for TSG-11 and TSG-12. In the past, an N-cycle method was used but is no longer preferred for the use of the interoperability testing.

For the Integrator's List test program jitter measurements are required to be made with HFTP and LBP, and if time permits should also be made with SSOP.

#### **Test Setup:**

The N5411A SATA compliance software will prompt for HFTP, LBP and/or SSOP when it needs those patterns. When prompted, if you will use the ULink DriveMaster 2006 software to put the device into BIST, follow this procedure:

- 1) Connect a SATA cable from the host system's port 0 SATA connection to the device under test.

- 2) Launch DriveMaster 2006 on the host system and choose the 'Ctl SATA' Control Panel icon from DriveMaster's menu bar. The default SATA Phy Control port is port 0.

- 3) From the BIST method combo box, choose the appropriate supported BIST method for communicating with the drive. For the 80-bit Transmit only test option with ALIGN bypass and scramble bypass, choose T+S+A; for the far-end retimed loopback mode, choose L.

- 4) For HFTP: In the User Patterns combo box, choose the High-Transition Density Pattern (HTDP). This is implemented as the HFTP, or 4A4A4A4A4 4A4A4A4A. Click the 'BIST' button to initiate the BIST command script, and wait for the status in the lower left-hand corner of the SATA Control Panel dialog to update to BIST FIS SUCCEEDED. If the status reads BIST FIS FAILED, click the COMRESET radio button and repeat steps 3-5.

- 5) Disconnect the SATA cable from the device and plug in the H303000204 test fixture. The H303000204 is connected to channels 1 and 3 of the DSO81204A/B by two 36" SMA cables (Rosenberger or equivalent). OBSERVE the signal on the scope. If it is correct, press OK in the N5411A prompt. If not, the device did not properly handle BIST Activate FIS; a non-standard way to make it produce the desired pattern will be required.

#### **Test Procedure:**

This parameter is covered by Agilent Technologies, Inc. N5411A automated SATA compliance software, revision 2.01 or later. Either "PASS" or "FAIL" is shown for the DJ at Connector, Data, 5UI test in the report generated at the completion of the testing.

#### **Observable Results:**

The DJ at Connector (Data, 5UI) value shall be less than 0.175 UI for Gen1i and Gen1m devices.

#### **Possible Problems:**

The SATA specification includes a pattern that makes LBP for RD+, and another if RD-. Since RD is not known, with either one there is a 50% chance that LBP will actually be produced correctly on the line. ULink's DriveMaster program provides both +ve and -ve versions of the LBP to ensure that this test can be performed correctly per the specification. The Agilent N5411A SATA compliance software will wait for the scope to trigger on and identify the 4-1-3 lone-bit pattern prior to performing the test. If the lone-bit cannot be identified, the N5411A will prompt you to try a different pattern. Return to the Test Setup section of this measurement and repeat steps 4 and 5, using the Lone-Bit Pattern (-ve) selection in the ULink DriveMaster software instead. After 2-3 BIST enable attempts with each pattern, you should be able to complete the Minimum Amplitude test. If not, a non-standard way to enable the Lone-Bit Pattern will be required.

#### Test TSG-09 - TJ at Connector, Data, 250UI

**Purpose:** To verify that the TJ at Connector (Data, 250UI) of the DUT's transmitter is within the conformance limits.

#### References:

- [1] SATA Standard, 7.2.1, Table 22 Transmitted Signal Requirements

- [2] Ibid, 7.2.2.3.11

- [3] Ibid, 7.4.8

- [4] SATA Interoperability Program Unified Test Document, 2.12.9 TJ at Connector, Data, 250UI

#### **Resource Requirements:**

Same as for TSG-01.

See appendix A for details.

**Last Template Modification:** May 7, 2006 (Version 2.01)

#### **Discussion:**

Reference [1] specifies the Transmitted Signal conformance limits for SATA devices. This specification includes conformance limits for the TJ at Connector (Data, 250UI). Reference [2] provides the definition of this term for the purposes of SATA testing. Reference [3] defines the measurement requirements for this test.

As noted directly in Reference [4], for components which support 3Gb/s, this requirement would be tested at 1.5Gb/s. For this test, the methodology of obtaining the result must follow a filtered TIE based method, similar to that for obtaining results for TSG-11 and TSG-12. Specifically, a second-order PLL with a loop bandwidth of (data rate / 500) and a damping factor of 0.707 is used to perform the clock recovery for measuring the time interval error prior to the jitter separation being performed. In the past, an N-cycle method was used but is no longer preferred for the use of the interoperability testing.

For the Integrator's List test program jitter measurements are required to be made with HFTP and LBP, and if time permits should also be made with SSOP.

#### **Test Setup:**

The N5411A SATA compliance software will prompt for HFTP, LBP and/or SSOP when it needs those patterns. When prompted, if you will use the ULink DriveMaster 2006 software to put the device into BIST, follow this procedure:

- 6) Connect a SATA cable from the host system's port 0 SATA connection to the device under test.

- 7) Launch DriveMaster 2006 on the host system and choose the 'Ctl SATA' Control Panel icon from DriveMaster's menu bar. The default SATA Phy Control port is port 0.

- 8) From the BIST method combo box, choose the appropriate supported BIST method for communicating with the drive. For the 80-bit Transmit only test option with ALIGN bypass and scramble bypass, choose T+S+A; for the far-end retimed loopback mode, choose L.

- 9) For HFTP: In the User Patterns combo box, choose the High-Transition Density Pattern (HTDP). This is implemented as the HFTP, or 4A4A4A4A4 4A4A4A4A. Click the 'BIST' button to initiate the BIST command script, and wait for the status in the lower left-hand corner of the SATA Control Panel dialog to update to BIST FIS SUCCEEDED. If the status reads BIST FIS FAILED, click the COMRESET radio button and repeat steps 3-5.

- 10) Disconnect the SATA cable from the device and plug in the H303000204 test fixture. The H303000204 is connected to channels 1 and 3 of the DSO81204A/B by two 36" SMA cables (Rosenberger or equivalent). OBSERVE the signal on the scope. If it is correct, press OK in the N5411A prompt. If not, the device did not properly handle BIST Activate FIS; a non-standard way to make it produce the desired pattern will be required.

#### **Test Procedure:**

This parameter is covered by Agilent Technologies, Inc. N5411A automated SATA compliance software, revision 2.01 or later. Either "PASS" or "FAIL" is shown for the TJ at Connector, Data, 250UI test in the report generated at the completion of the testing.

#### **Observable Results:**

The TJ at Connector (Data, 250UI) value shall be less than 0.47 UI for Gen1i and Gen1m devices.

#### **Possible Problems:**

The SATA specification includes a pattern that makes LBP for RD+, and another if RD-. Since RD is not known, with either one there is a 50% chance that LBP will actually be produced correctly on the line. ULink's DriveMaster program provides both +ve and -ve versions of the LBP to ensure that this test can be performed correctly per the specification. The Agilent N5411A SATA compliance software will wait for the scope to trigger on and identify the 4-1-3 lone-bit pattern prior to performing the test. If the lone-bit cannot be identified, the N5411A will prompt you to try a different pattern. Return to the Test Setup section of this measurement and repeat steps 4 and 5, using the Lone-Bit Pattern (-ve) selection in the ULink DriveMaster software instead. After 2-3 BIST enable attempts with each pattern, you should be able to complete the Minimum Amplitude test. If not, a non-standard way to enable the Lone-Bit Pattern will be required.

#### Test TSG-10 - DJ at Connector, Data, 250UI

**Purpose:** To verify that the DJ at Connector (Data, 250UI) of the DUT's transmitter is within the conformance limits.

#### References:

- [1] SATA Standard, 7.2.1, Table 22 Transmitted Signal Requirements

- [2] Ibid, 7.2.2.3.11

- [3] Ibid, 7.4.8

- [4] SATA Interoperability Program Unified Test Document, 2.12.01 DJ at Connector, Data, 250UI

#### **Resource Requirements:**

Same as for TSG-01.

See appendix A for details.

**Last Template Modification:** May 7, 2006 (Version 2.01)

#### **Discussion:**

Reference [1] specifies the Transmitted Signal conformance limits for SATA devices. This specification includes conformance limits for the DJ at Connector (Data, 250UI). Reference [2] provides the definition of this term for the purposes of SATA testing. Reference [3] defines the measurement requirements for this test.

As noted directly in Reference [4], for components which support 3Gb/s, this requirement would be tested at 1.5Gb/s. For this test, the methodology of obtaining the result must follow a filtered TIE based method, similar to that for obtaining results for TSG-11 and TSG-12. Specifically, a second-order PLL with a loop bandwidth of (data rate / 500) and a damping factor of 0.707 is used to perform the clock recovery for measuring the time interval error prior to the jitter separation being performed. In the past, an N-cycle method was used but is no longer preferred for the use of the interoperability testing.

For the Integrator's List test program jitter measurements are required to be made with HFTP and LBP, and if time permits should also be made with SSOP.

#### **Test Setup:**

The N5411A SATA compliance software will prompt for HFTP, LBP and/or SSOP when it needs those patterns. When prompted, if you will use the ULink DriveMaster 2006 software to put the device into BIST, follow this procedure:

- 11) Connect a SATA cable from the host system's port 0 SATA connection to the device under test.

- 12) Launch DriveMaster 2006 on the host system and choose the 'Ctl SATA' Control Panel icon from DriveMaster's menu bar. The default SATA Phy Control port is port 0.

- 13) From the BIST method combo box, choose the appropriate supported BIST method for communicating with the drive. For the 80-bit Transmit only test option with ALIGN bypass and scramble bypass, choose T+S+A; for the far-end retimed loopback mode, choose L.

- 14) For HFTP: In the User Patterns combo box, choose the High-Transition Density Pattern (HTDP). This is implemented as the HFTP, or 4A4A4A4A4 4A4A4A4Ah. Click the 'BIST' button to initiate the BIST command script, and wait for the status in the lower left-hand corner of the SATA Control Panel dialog to update to BIST FIS SUCCEEDED. If the status reads BIST FIS FAILED, click the COMRESET radio button and repeat steps 3-5.

- 15) Disconnect the SATA cable from the device and plug in the H303000204 test fixture. The H303000204 is connected to channels 1 and 3 of the DSO81204A/B by two 36" SMA cables (Rosenberger or equivalent). OBSERVE the signal on the scope. If it is correct, press OK in the N5411A prompt. If not, the device did not properly handle BIST Activate FIS; a non-standard way to make it produce the desired pattern will be required.

#### **Test Procedure:**

This parameter is covered by Agilent Technologies, Inc. N5411A automated SATA compliance software, revision 2.01 or later. Either "PASS" or "FAIL" is shown for the DJ at Connector, Data, 250UI test in the report generated at the completion of the testing.

#### **Observable Results:**

The DJ at Connector (Data, 250UI) value shall be less than 0.22 UI for Gen1i and Gen1m devices.

#### **Possible Problems:**

The SATA specification includes a pattern that makes LBP for RD+, and another if RD-. Since RD is not known, with either one there is a 50% chance that LBP will actually be produced correctly on the line. ULink's DriveMaster program provides both +ve and -ve versions of the LBP to ensure that this test can be performed correctly per the specification. The Agilent N5411A SATA compliance software will wait for the scope to trigger on and identify the 4-1-3 lone-bit pattern prior to performing the test. If the lone-bit cannot be identified, the N5411A will prompt you to try a different pattern. Return to the Test Setup section of this measurement and repeat steps 4 and 5, using the Lone-Bit Pattern (-ve) selection in the ULink DriveMaster software instead. After 2-3 BIST enable attempts with each pattern, you should be able to complete the Minimum Amplitude test. If not, a non-standard way to enable the Lone-Bit Pattern will be required.

#### Test TSG-11 - TJ at Connector, Clock, 500

**Purpose:** To verify that the TJ at Connector (Clock, 500) of the DUT's transmitter is within the conformance limits.

#### References:

- [1] SATA Standard, 7.2.1, Table 22 Transmitted Signal Requirements

- [2] Ibid, 7.2.2.3.12

- [3] Ibid, 7.4.6, 7.4.8

- [4] SATA Interoperability Program Unified Test Document, 2.12.11 TJ at Connector, Clock, 500

#### **Resource Requirements:**

Same as for TSG-01

See appendix A for details.

**Last Template Modification:** May 7, 2006 (Version 2.01)

#### **Discussion:**

Reference [1] specifies the Transmitted Signal conformance limits for SATA devices. This specification includes conformance limits for the TJ at Connector (Clock, 500). Reference [2] provides the definition of this term for the purposes of SATA testing. Reference [3] defines the measurement requirements for this test.

This test applies to Gen2i (3.0Gbps) devices. Since estimating TJ at a BER of 10^-12 requires first separating DJ from the higher error probability CDF, TSG-11 and TSG-12 results are measured at the same time.

For the Integrator's List test program jitter measurements are required to be made with HFTP and LBP, and if time permits should also be made with SSOP.

#### **Test Setup:**

The N5411A SATA compliance software will prompt for HFTP, LBP and/or SSOP when it needs those patterns. When prompted for these patterns, if you will use the ULink DriveMaster 2006 software to put the device into BIST, follow this procedure:

- 1) Connect a SATA cable from the host system's port 0 SATA connection to the device under test.

- 2) Launch DriveMaster 2006 on the host system and choose the 'Ctl SATA' Control Panel icon from DriveMaster's menu bar. The default SATA Phy Control port is port 0.

- 3) From the BIST method combo box, choose the appropriate supported BIST method for communicating with the drive. For the 80-bit Transmit only test option with ALIGN bypass and scramble bypass, choose T+S+A; for the far-end retimed loopback mode, choose L.

- 4) For HFTP: In the User Patterns combo box, choose the High-Transition Density Pattern (HTDP). This is implemented as the HFTP, or 4A4A4A4A4 4A4A4A4A. For LBP: In the User Patterns combo box, choose the Lone-Bit Pattern (+ve) selection. This is implemented as 8BFC8DFCh 8EFC8BFCh. For SSOP: In the User Patterns combo box, choose the SSOP selection. This is implemented as 7F7F7F7Fh 7F7F7Fh.

- 5) Click the 'BIST' button to initiate the BIST command script, and wait for the status in the lower left-hand corner of the SATA Control Panel dialog to update to BIST FIS SUCCEEDED. If the status reads BIST FIS FAILED, click the COMRESET radio button and repeat steps 3-5.

- 6) Disconnect the SATA cable from the device and plug in the H303000204 test fixture. The H303000204 is connected to channels 1 and 3 of the DSO81204A/B by two 36" SMA cables (Rosenberger or equivalent). OBSERVE the signal on the scope. If it is correct, press OK in the N5411A prompt. If not, the device did not properly handle BIST Activate FIS; a non-standard way to make it produce the desired pattern will be required.

#### **Test Procedure:**

This parameter is covered by Agilent Technologies, Inc. N5411A automated SATA compliance software, revision 2.01 or later. Either "PASS" or "FAIL" is shown for the Gen II TJ test in the report generated at the completion of the testing.

### **Observable Results:**

The TJ shall be less than 0.37UI when measured at  $f_{BAUD}/500$  for 3.0GB/s devices.

### **Possible Problems:**

The SATA specification includes a pattern that makes LBP for RD+, and another if RD-. Since RD is not known, with either one there is a 50% chance that LBP will actually be produced correctly on the line. ULink's DriveMaster program provides both +ve and -ve versions of the LBP to ensure that this test can be performed correctly per the specification. The Agilent N5411A SATA compliance software will wait for the scope to trigger on and identify the 4-1-3 lone-bit pattern prior to performing the test. If the lone-bit cannot be identified, the N5411A will prompt you to try a different pattern. Return to the Test Setup section of this measurement and repeat steps 4 and 5, using the Lone-Bit Pattern (-ve) selection in the ULink DriveMaster software instead. After 2-3 BIST enable attempts with each pattern, you should be able to complete the Minimum Amplitude test. If not, a non-standard way to enable the Lone-Bit Pattern will be required.

### Test TSG-12 - DJ at Connector, Clock, 500

**Purpose:** To verify that the DJ at Connector (Clock, 500) of the DUT's transmitter is within the conformance limits.

### **References:**

- [1] SATA Standard, 7.2.1, Table 22 Transmitted Signal Requirements

- [2] Ibid, 7.2.2.3.12

- [3] Ibid, 7.4.6, 7.4.8

- [4] SATA Interoperability Program Unified Test Document, 2.12.12 DJ at Connector, Clock, 500

## **Resource Requirements:**

Same as for TSG-01.

See appendix A for details.

**Last Template Modification:** May 7, 2006 (Version 2.01)

### **Discussion:**

Reference [1] specifies the Transmitted Signal conformance limits for SATA devices. This specification includes conformance limits for the DJ at Connector (Clock, 500). Reference [2] provides the definition of this term for the purposes of SATA testing. Reference [3] defines the measurement requirements for this test.

This test applies to Gen2i (3.0Gbps) devices. Since estimating TJ at a BER of 10^-12 requires first separating DJ from the higher error probability CDF, TSG-11 and TSG-12 results are measured at the same time.

For the Integrator's List test program jitter measurements are required to be made with HFTP and LBP, and if time permits should also be made with SSOP.

## **Test Setup:**

This test result is derived at the same time as TSG-11. Therefore, no setup change is needed for TSG-12.

## **Test Procedure:**

This parameter is covered by Agilent Technologies, Inc. N5411A automated SATA compliance software, revision 2.01 or later. Either "PASS" or "FAIL" is shown for the Gen II TJ test in the report generated at the completion of the testing.

### **Observable Results:**

The DJ shall be less than 0.19UI when measured at  $f_{BAUD}/500$  for 3.0GB/s devices.

### **Possible Problems:**

The SATA specification includes a pattern that makes LBP for RD+, and another if RD-. Since RD is not known, with either one there is a 50% chance that LBP will actually be produced correctly on the line. ULink's DriveMaster program provides both +ve and -ve versions of the LBP to ensure that this test can be performed correctly per the specification. The Agilent N5411A SATA compliance software will wait for the scope to trigger on and identify the 4-1-3 lone-bit pattern prior to performing the test. If the lone-bit cannot be identified, the N5411A will prompt you to try a different pattern. Return to the Test Setup section of this measurement and repeat steps 4 and 5, using the Lone-Bit Pattern (-ve) selection in the ULink DriveMaster software instead. After 2-3 BIST enable attempts with each pattern, you should be able to complete the Minimum Amplitude test. If not, a non-standard way to enable the Lone-Bit Pattern will be required.

# **GROUP 3: PHY OOB REQUIREMENTS**

# Overview:

This group of tests verifies the Phy OOB Requirements, as defined in Section 2.15 of the SATA Interoperability Unified Test Document, v0.9 (which references the SATA Standard, v2.5).

## Test OOB-01 - OOB Signal Detection Threshold

**Purpose:** To verify that the OOB Signal Detection Threshold of the DUT's receiver is within the conformance limits.

### **References:**

- [1] SATA Standard, 7.2.1, Table 25 OOB Specifications

- [2] Ibid, 7.2.2.7.1

- [3] Ibid, 7.4.20

- [4] SATA Interoperability Program Unified Test Document, 2.14.1 OOB Signal Detection Threshold

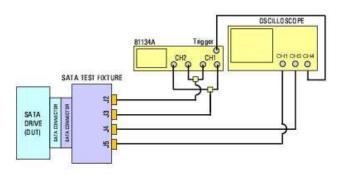

### **Resource Requirements:**

Agilent DSO81204A/B (12GHz bandwidth, 40GS/s per channel on 2 channels) with

Agilent N5411A SATA Electrical Performance Validation and Compliance Test Software

COMAX iSATA(cable connector) to SMA(f) test fixture distributed by CRUZ Systems (H303000204)

Agilent 81134A 2-channel 3.35GHz Pulse/Pattern Generator

Agilent 33340C 20dB DC-26.5GHz Passive Attenuator (Qty. 2 needed)

Agilent 11636B Power Divider (not power splitter) DC-26.5GHz (Qty. 2 needed)

Agilent 5062-6681 6-inch SMA cable (Qty. 4 needed to mix 81134A outputs for OOB testing)

Agilent 1169A 13GHz Differential Active Voltage Probe with

N5381A 13GHz Differential Solder-In Probe Head (to verify differential amplitude of signal delivered to the differential RX input on the device under test and monitor the Device TX Output response) (Qty. 2 needed)

See appendix A for details.

**Last Template Modification:** May 7, 2006 (Version 2.01)

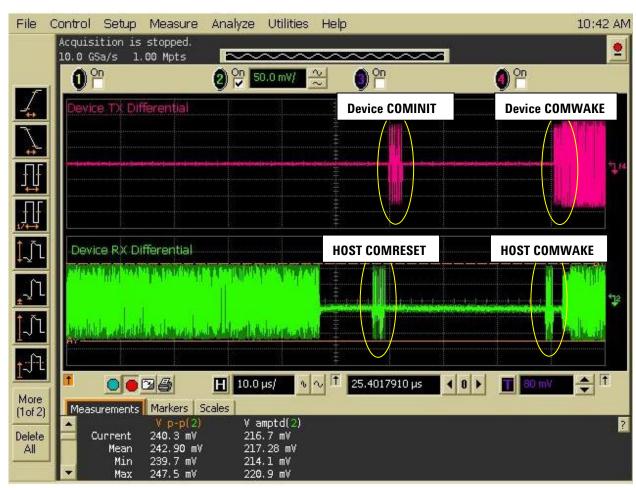

## **Discussion:**